The PowerPC Core

MOTOROLA

MPC823e REFERENCE MANUAL

6-15

CORE

6

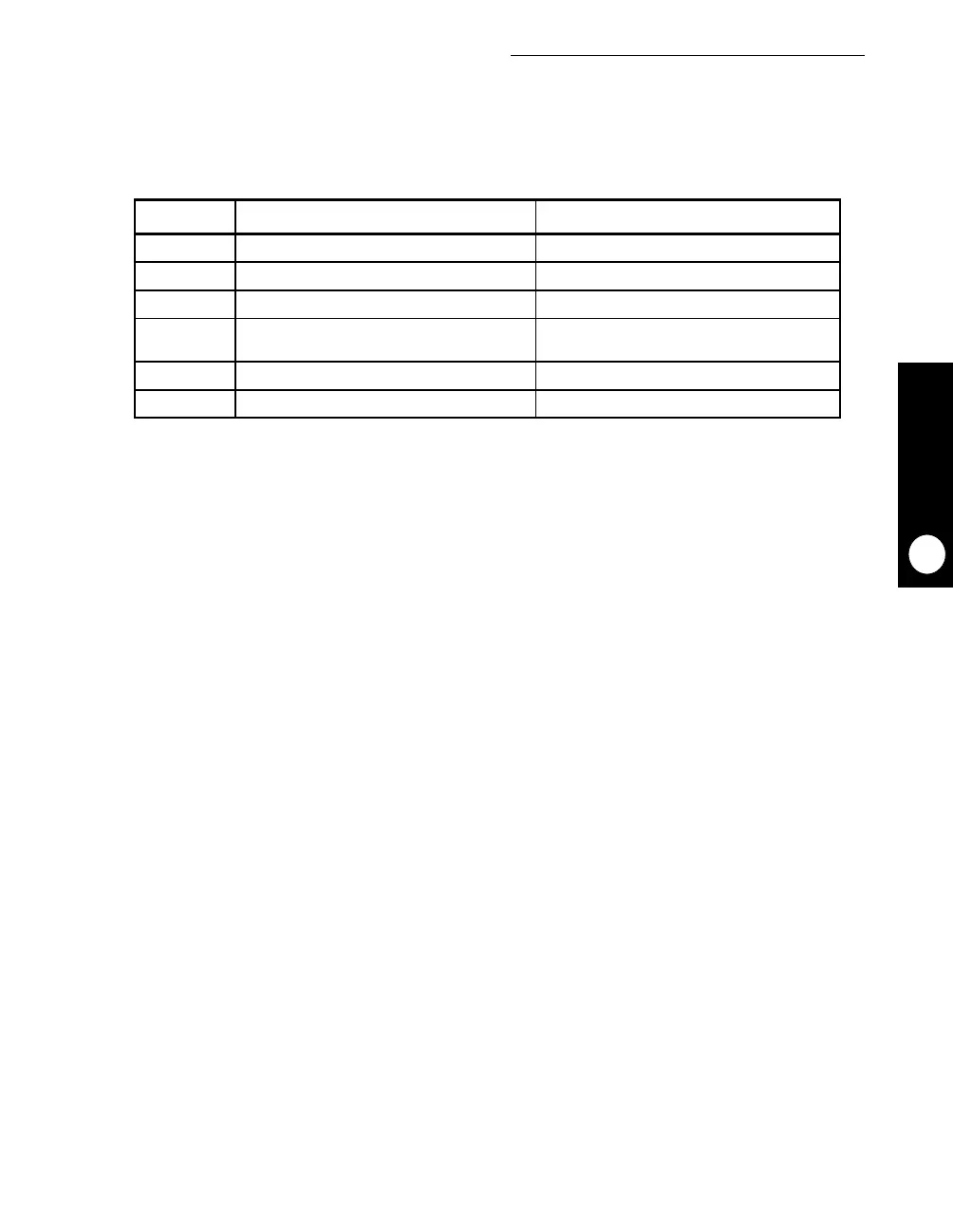

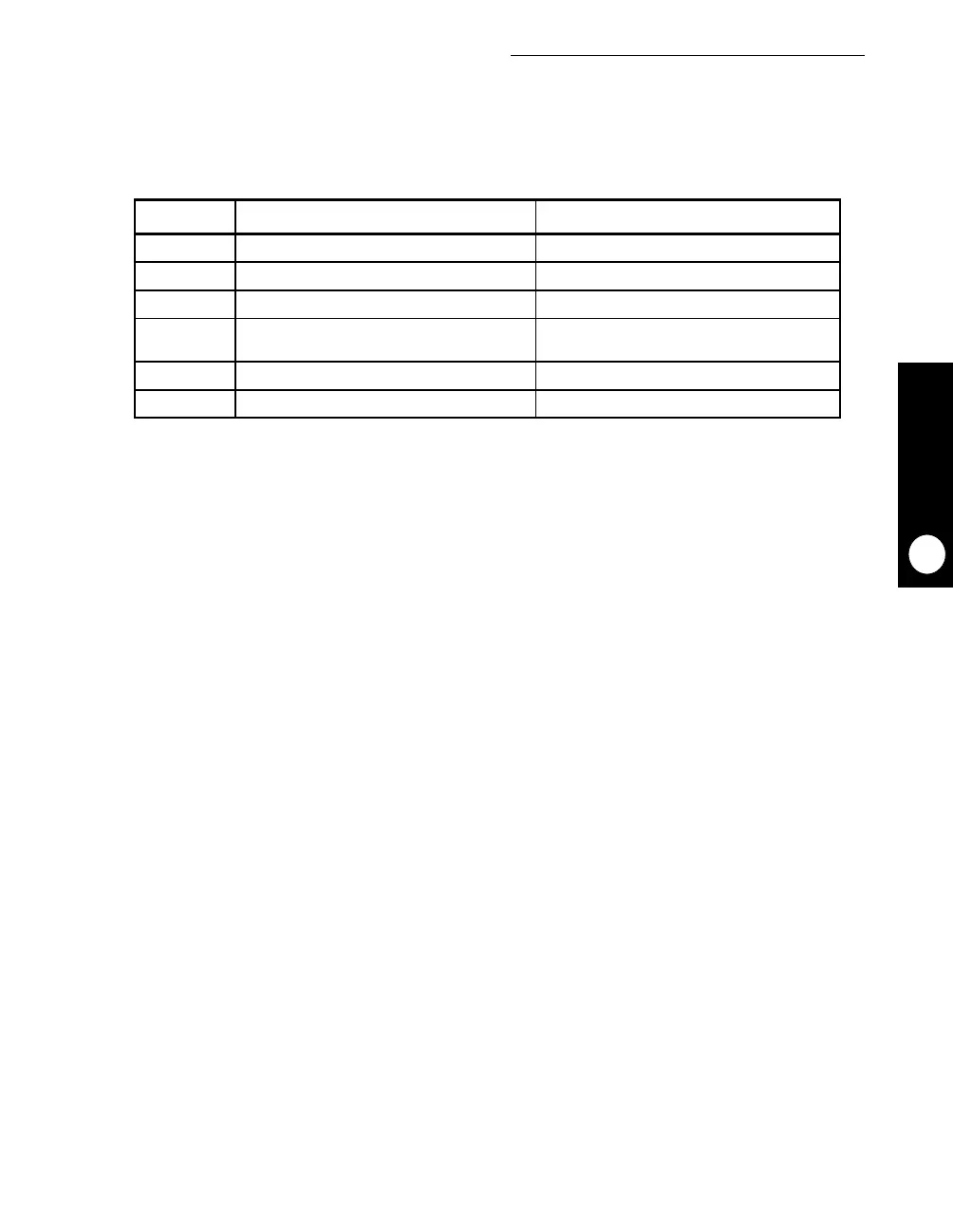

More than one asynchronous interrupt cause or exception can be present at any time.

However, when more than one interrupt causes exist, only the highest priority interrupt is

taken, as shown in the following table.

6.4 THE REGISTER UNIT

The fixed-point registers bank holds thirty-two 32-bit fixed-point registers and some control

registers. The register unit holds the general register files of the core and performs the

following operations:

• Decodes the operand fields of all sequential instructions

• Drives the operand buses, as requested by the execution unit

• Performs scoreboard checking and signing

• Samples the resulting data from the writeback bus

Table 6-6. Interrupt Priority Mapping

NUMBER INTERRUPT TYPE CAUSE

1 Development Port Nonmaskable Interrupt Signal from the Development Port

2 System Reset NMI_L Assertion

3 Instruction-Related Interrupts Instruction Processing

4 Peripheral Breakpoint Request or

Development Port Maskable Interrupt

Breakpoint Signal from any Peripheral

5 External Interrupt Signal from the Interrupt Controller

6 Decrementer Interrupt Decrementer Request

Loading...

Loading...