Development Capabilities and Interface

20-10

MPC823e REFERENCE MANUAL

MOTOROLA

DEVELOPMENT

20

CAPABILITIES & INTERFACE

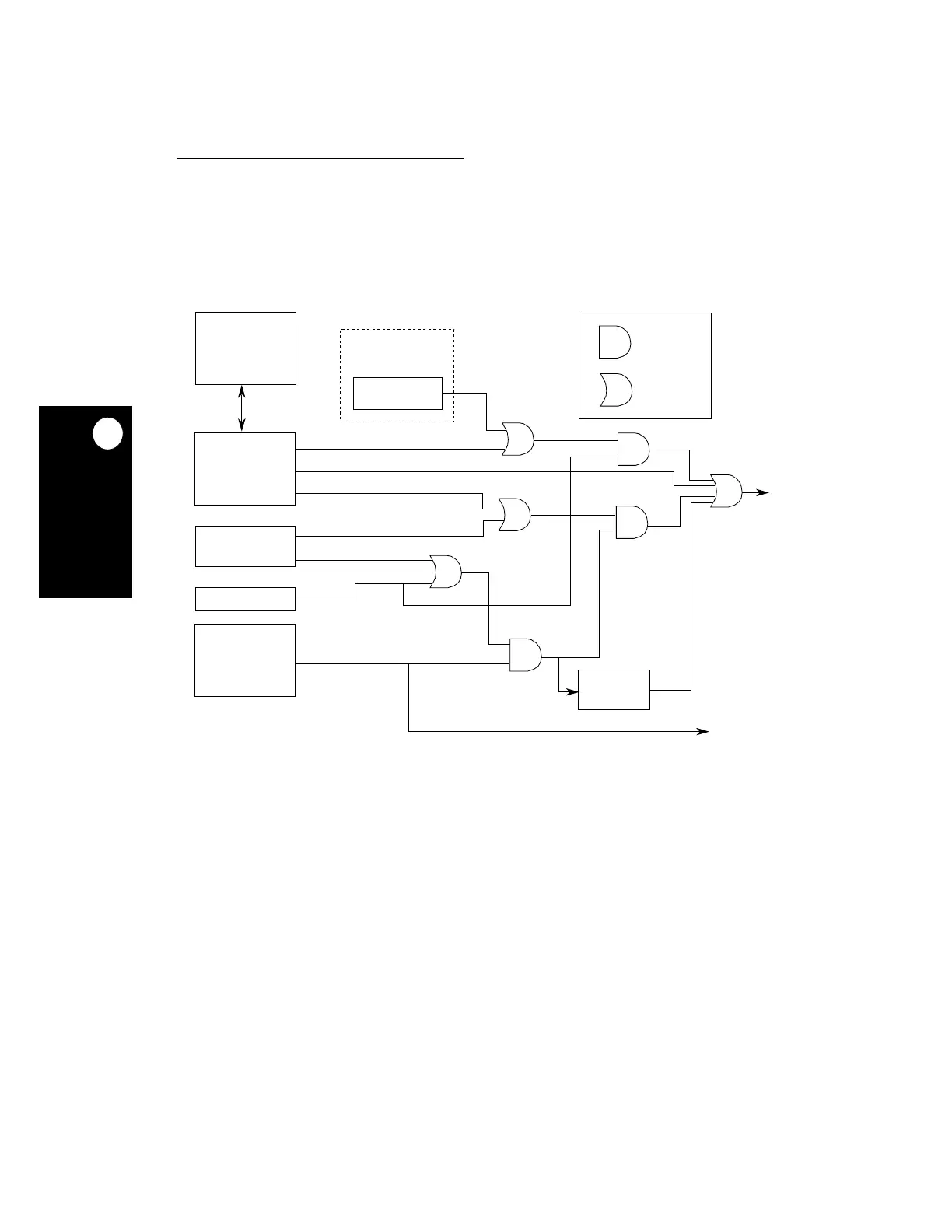

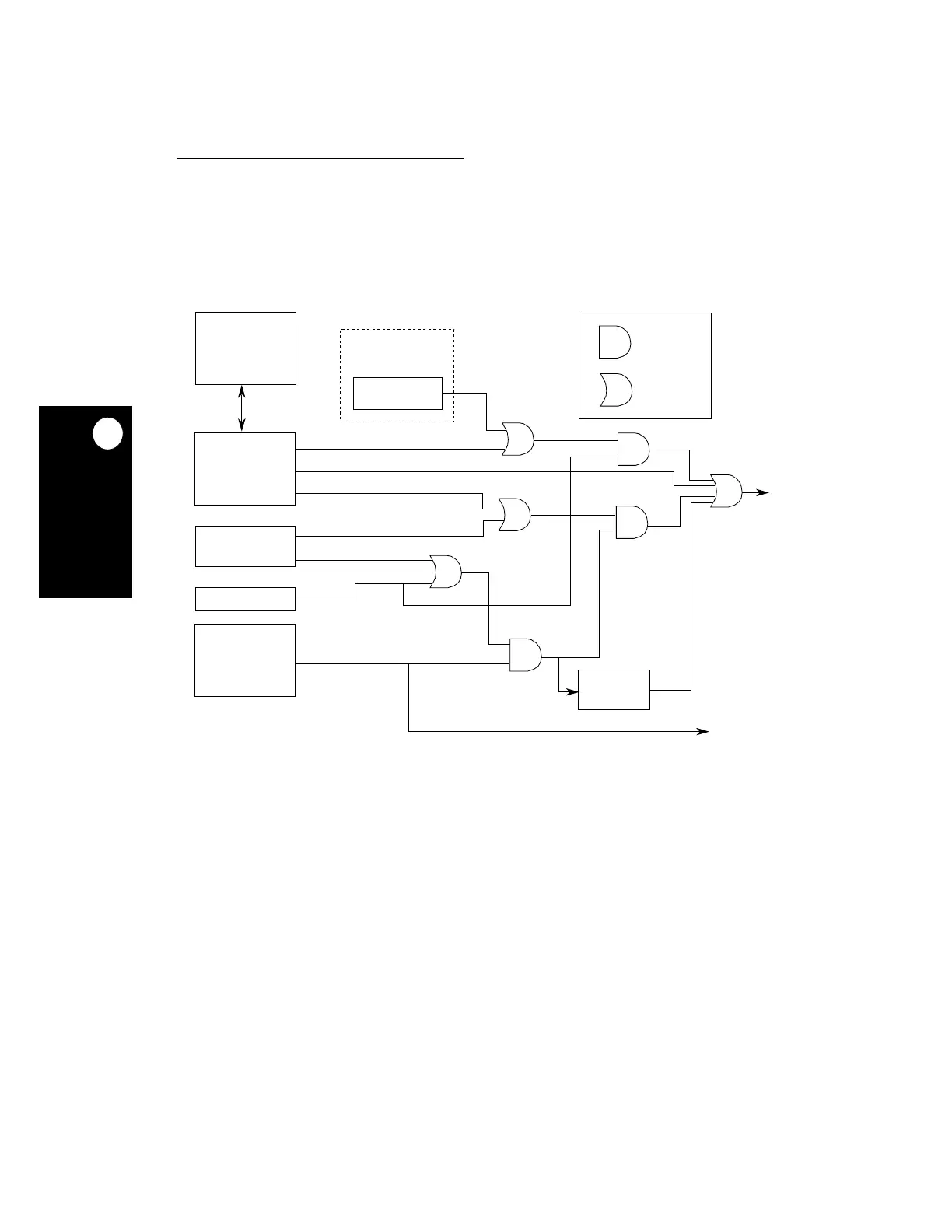

Greater-than-or-equal-to and less-than-or-equal-to are easily obtained from these four

conditions. Refer to

Section 20.3.1.5 Generating Compare Types

for more information.

Using the AND-OR logic structures “in range” and “out of range”, detections of address and

data comparators are supported. Using the counters, you can program a breakpoint to be

recognized after an event has been detected after a predefined number of times.

The L-data comparators operate on load or store fixed-point data. When operating on

fixed-point data, the L-data comparators perform a comparison on bytes, half-words, and

words. They treat numbers as either signed or unsigned values. The comparators generate

match events and then instruction match events enter the instruction AND-OR logic where

the instruction watchpoints and breakpoint are generated. The asserted instruction

watchpoints can generate the instruction breakpoint. Two different events can decrement

one of the counters. When a counter on one of the instruction watchpoints expires, the

instruction breakpoint is asserted.

Figure 20-1. Watchpoint and Breakpoint Support in the Core

INTERNAL

PERIPHERALS

X

X

X

X

DEVELOPMENT

SYSTEM OR

EXTERNAL

PERIPHERALS

DEVELOPMENT

PORT

LCTRL2

MSR

INTERNAL

WATCHPOINTS

LOGIC

WATCHPOINTS

MSR

RI

NONMASKED CONTROL BIT

SOFTWARE TRAP ENABLE BITS

DEVELOPMENT PORT TRAP ENABLE BITS

NONMASKABLE BREAKPOINT

MASKABLE BREAKPOINT

CPM

µ

CODE

DEVELOPMENT

ACCESSIBLE

BIT WISE AND

BIT WISE OR

COUNTERS

BREAKPOINT

TO CPU

TO

WATCHPOINT

PINS

Loading...

Loading...