Development Capabilities and Interface

20-14 MPC823e REFERENCE MANUAL MOTOROLA

DEVELOPMENT

20

CAPABILITIES & INTERFACE

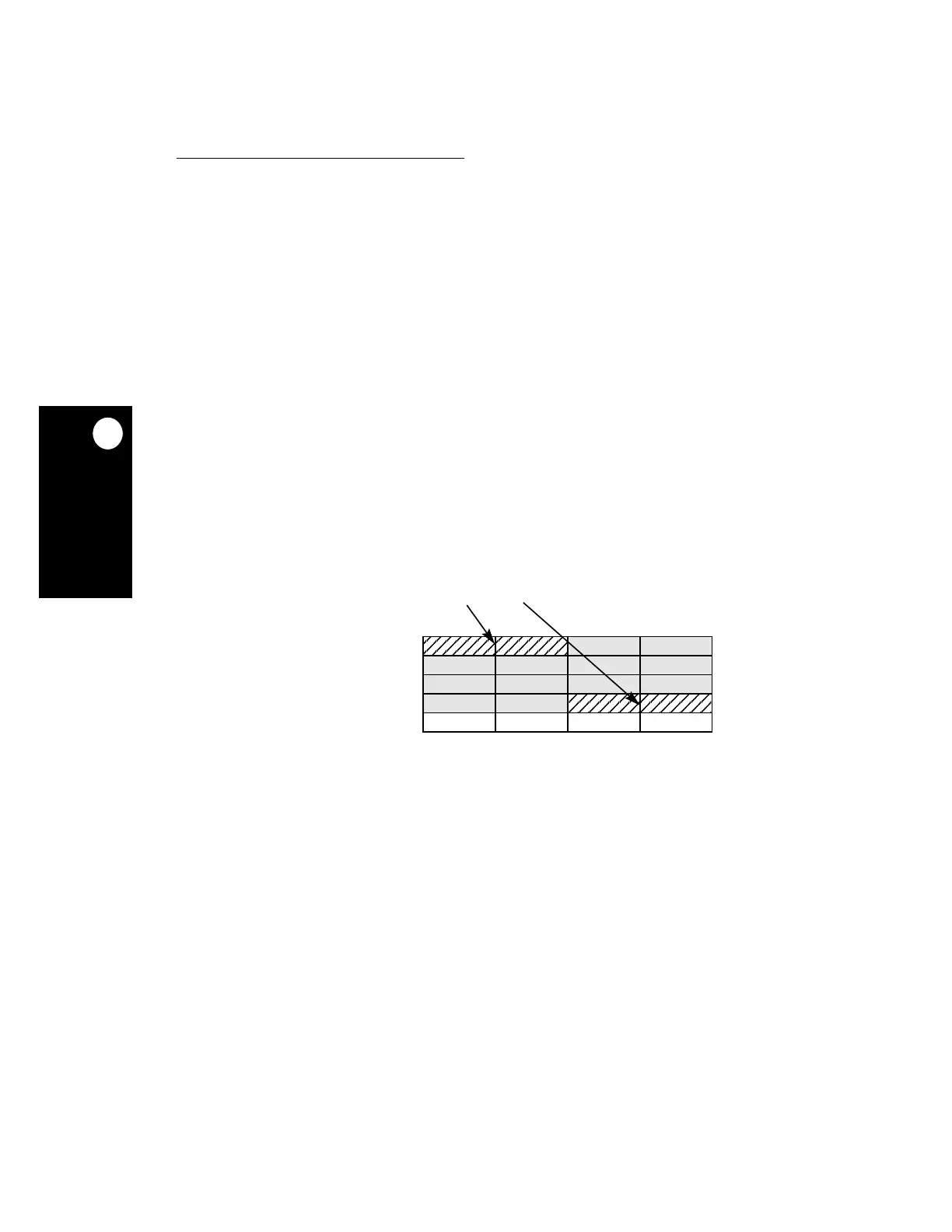

Half-Word Working Mode Example 2

Data size: Half-word.

Address: Greater than or equal to 0x00000002 and less than 0x0000000e.

Data value: Greater than 0x4e204e20 and less than 0x9c409c40.

Programming option:

One L-address comparator = 0x00000001 and program for greater than.

One L-address comparator = 0x0000000e and program for less than.

One L-data comparator = 0x4e204e20 and program for greater than.

One L-data comparator = 0x9c409c40 and program for less than.

CGBMSK and CHBMSK fields of the LCTRL1 = 0xe.

Both L-data comparators program to half-word or word mode.

Result:

The event will be correctly detected if the compiler chooses a load/store instruction with

a data size of half-word. If the compiler chooses load/store instructions with a data size

greater than half-word (word, multiple), there might be some false detections.

This example uses Figure 20-2 to show the possible false detects that must be ignored by

the software that handles the breakpoints.

20.3.1.3 CONTEXT-DEPENDENT FILTER. The core can only be programmed to

recognize internal breakpoints when the MSR

RI

bit is set or to always recognize internal

breakpoints. When it is programmed only to recognize internal breakpoints or when

MSR

RI

= 1, all parts of the code can be debugged, except when the save and restore

register 0 (SRR0), save and restore register 1 (SRR1), data address register (DAR), and

data storage interrupt status register (DSISR) are busy and MSR

RI

= 0.

Figure 20-2. Example 2 False Detect on Watchpoint/Breakpoint

0X00000000

0X00000004

0X00000008

0X0000000C

0X00000010

POSSIBLE FALSE DETECT ON THESE HALF-WORDS WHEN USING WORD/MULTIPLE

Loading...

Loading...