Development Capabilities and Interface

MOTOROLA MPC823e REFERENCE MANUAL 20-57

DEVELOPMENT

20

CAPABILITIES & INTERFACE

LBRK—Load/Store Breakpoint Interrupt

This bit is set as a result of the assertion of an load/store breakpoint. The core enters debug

mode if enabled and the LBRKE bit in the DER is set.

IBRK—Instruction Breakpoint Interrupt

This bit is set as a result of the assertion of an instruction breakpoint. The core enters debug

mode if enabled and the IBRKE bit in the DER is set.

EBRK—External Breakpoint Interrupt

This bit is set as a result of the assertion of an external breakpoint. The core enters debug

mode if enabled and the EBRKE bit in the DER is set.

DPI—Development Port Interrupt

This bit is set by the development port as a result of a debug station nonmaskable request

or when entering debug mode immediately out of reset. The core enters debug mode if

enabled and the DPIE bit in the DER is set.

20.6.3.2 DEBUG ENABLE REGISTER. The debug enable register (DER) allows the

enabling of events that cause the processor to enter debug mode.

Bits 0, 4, and 5—Reserved

These bits are reserved and must be set to 0.

RSTE—Reset Interrupt Enable

0 = Debug mode entry is disabled (reset value).

1 = Debug mode entry is enabled.

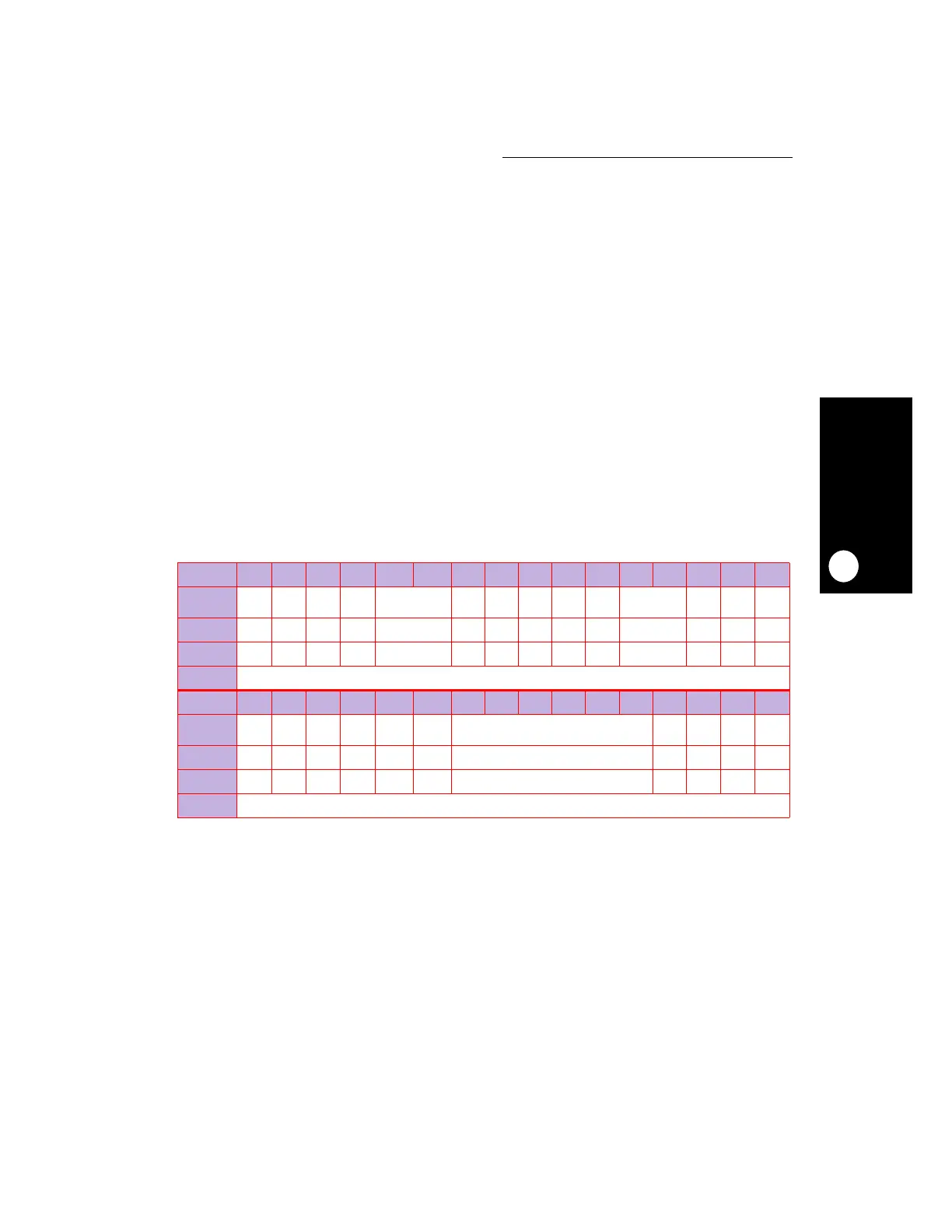

DER

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

RES RSTE

CHSTP

E

MCIE RESERVED EXTIE ALIE PRIE

FPUVI

E

DECIE RESERVED SYSIE TRE RES

RESET

0010 0 00000 0 010

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

SPR

149

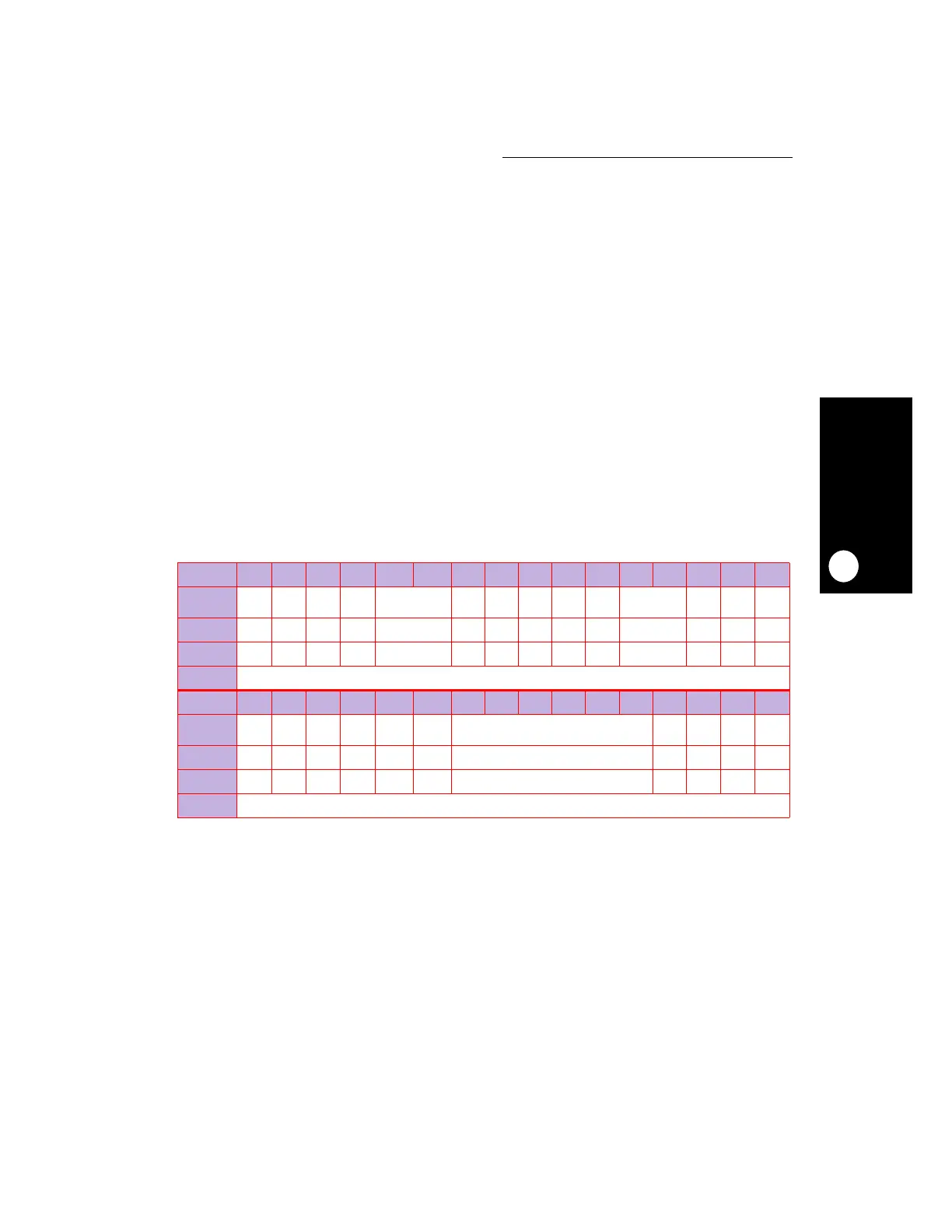

BIT 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

RES SEIE

ITLBMS

E

DTLBM

SE

ITLBERE

DTLBER

E

RESERVED LBRKE IBRKE EBRKE DPIE

RESET

0000 0 0 0 1111

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

SPR

149

Loading...

Loading...