Clocks and Power Control

MOTOROLA

MPC823e REFERENCE MANUAL

5-15

CLOCKS AND POWER

5

CONTROL

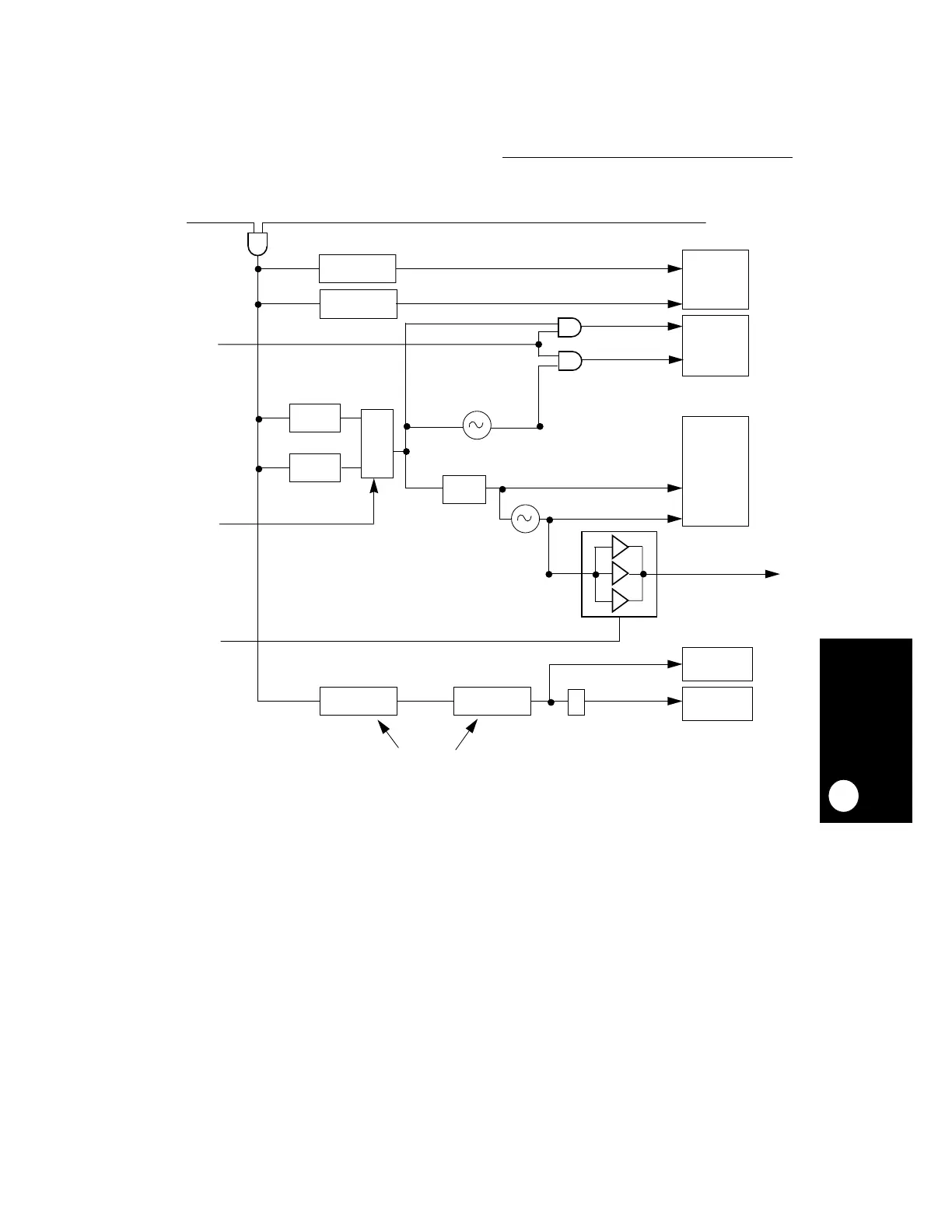

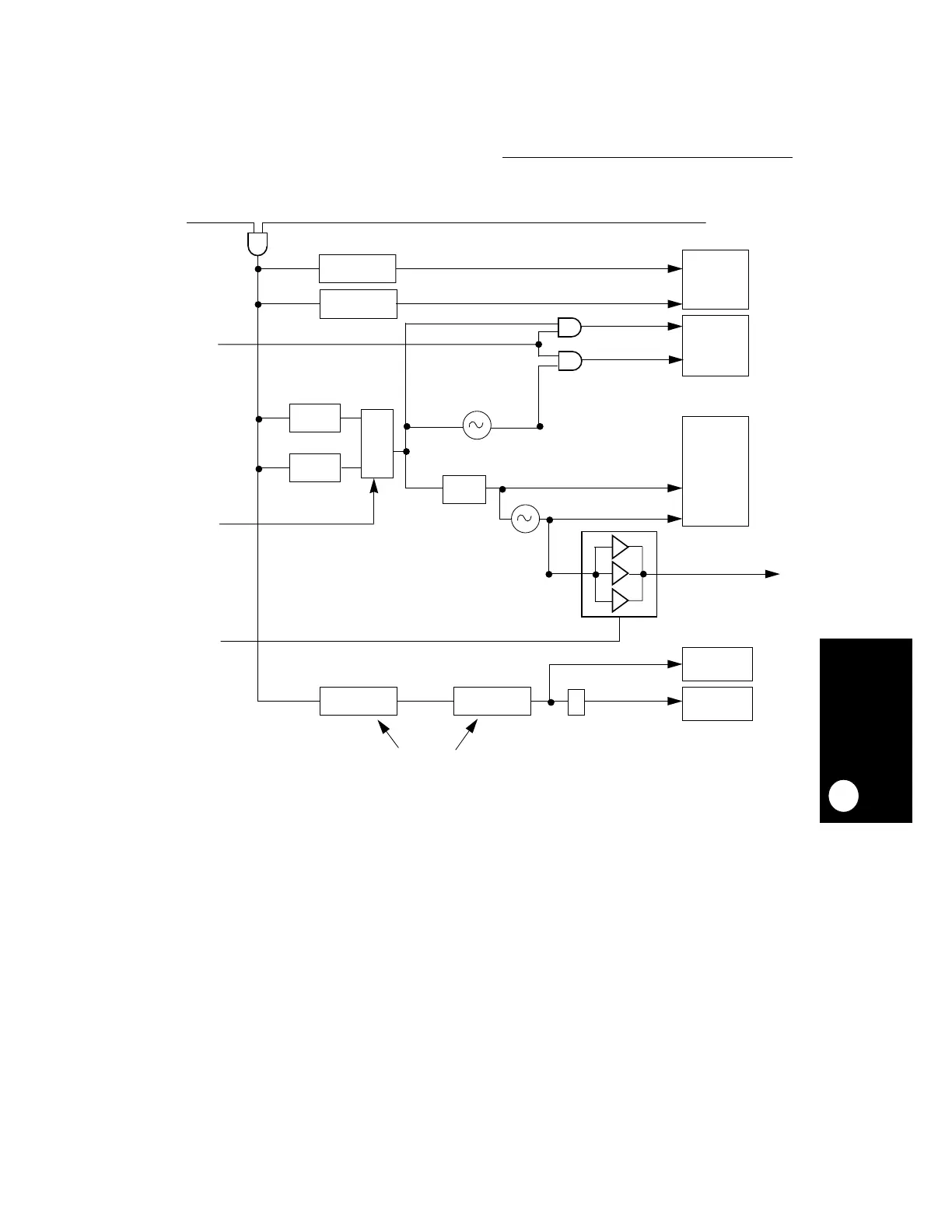

The low-power dividers allow you to reduce and restore the operating frequencies of

different sections of the MPC823e without losing the SPLL lock. Using the low-power

dividers, you can still obtain full chip operation, but at a lower frequency. This is called

normal low mode. You can switch to normal low mode or set the speed at any time and the

changes you make will occur immediately. The low-power dividers are controlled by the

SCCR and its default division factor is divide by one at reset. For a 40MHz system,

SYNCCLK, LCDCLK, LCDCLK50, BRGCLK, and GCLKx are all 40MHz at reset.

Figure 5-5. Clock Dividers

DFSYNC

DFBRG

DFNH

DFNL

DFLCD DFALCD

2:1

MUX

EBDF

CPM

CORE

UPM,

EXTERNAL

LCD/VIDEO

CONTROLLER

LCD PANEL

SYNCCLK

BRGCLK

GCLK1C

GCLK2C

GCLK2

GCLK1_50

GCLK2_50

CLKOUT

LCDCLK

LCDCLK50

DIVISION FACTOR TOTAL LESS THAN 64

LOW-POWER MODE

PHASE

PHASE

BUS

INTERFACE

NORMAL MODES

NORMAL OR

DOZE MODE

COM[0:1]

GCLK1

PCMCIA,

Loading...

Loading...