Serial Communication Performance

MOTOROLA

MPC823e REFERENCE MANUAL

A-3

SERIAL COMMUNICATION

A

PERFORMANCE

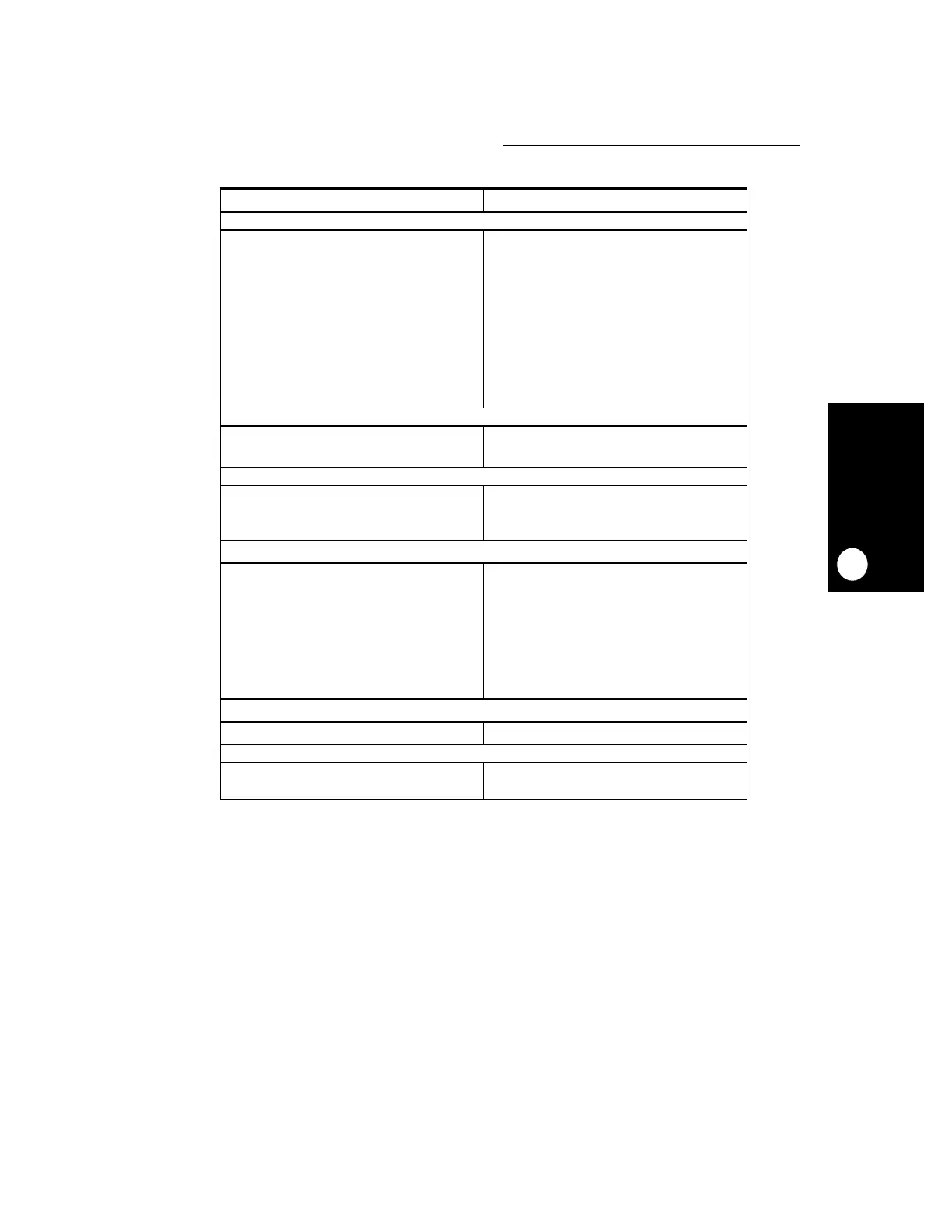

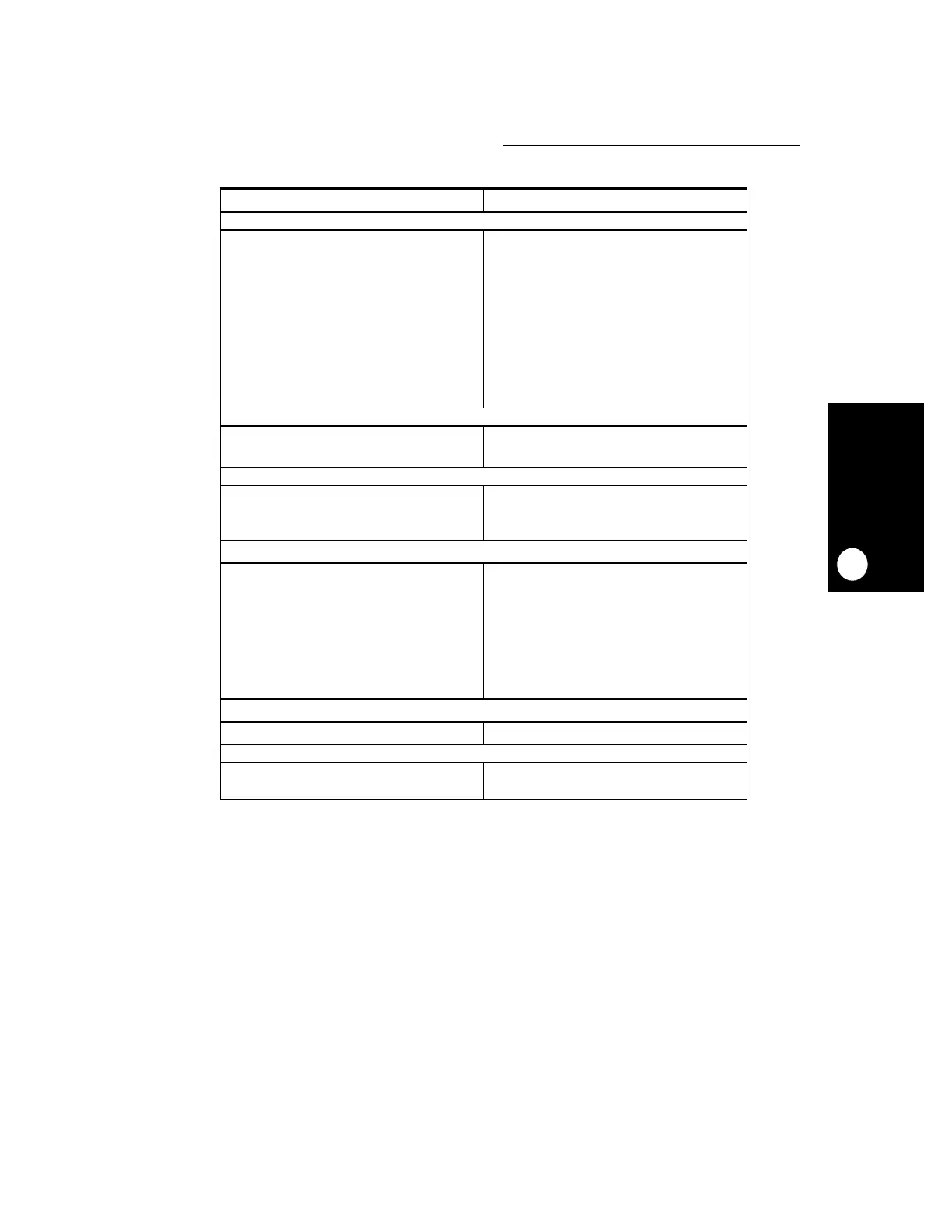

Table A-1. MPC823e Performance Table

CONTROLLER/PROTOCOL CPM PERFORMANCE FACTOR

SCC

Ethernet (Half-Duplex) 22,000 Kbps

Ethernet (Full-Duplex) 11,000 Kbps

HDLC (Full-Duplex) 8,000 Kbps

Transparent (Full-Duplex) 8,000 Kbps

UART (Full-Duplex) 2,400 Kbd

Async HDLC (Full-Duplex) 3,000 Kbps

IrDA High-Speed

1

16,000 Kbps

IrDA Medium-Speed

2

16,000 Kbps

IrDA Low-Speed

3

6,000 Kbps

SPI (Half-Duplex)

SPI Byte 500 Kbps

SPI Word

4

3,125 Kbps

SMC

Transparent (Full-Duplex) 1,500 Kbps

UART (Half-Duplex) 440 Kbd

UART (Full-Duplex) 220 Kbd

IDMA

5

Memory->Peripheral (Dual-Address Mode)

5

1,600 KBps

Peripheral->Memory (Dual-Address Mode)

5

2,200 KBps

Memory->Memory

6

5,700 KBps

Memory->Memory (BURST)

6

10,400 KBps

Memory->Peripheral (Single-Address Mode)

6

5,000 KBps

Peripheral->Memory (Single-Address Mode)

6

5,000 KBps

I

2

C (Half-Duplex)

I

2

C

2,080 Kbps

USB

USB High-Speed 24,000 Kbps

USB Low-Speed 24,000 Kbps

1. Same as Transparent Half-Duplex.

2. Same as HDLC Half-Duplex.

3. Same as Asynchronous HDLC Half-Duplex.

4. The SPI controller is in Word mode if the data character is greater than 8 bits in length.

5. The CPM performance factor assumes a 32-bit peripheral port size. The CPM

performance for 16- and 8-bit port sizes would be one-quarter and one-half of those

listed.

6. The CPM performance factor is independent of port size. The CPM performance factor

is identical for 8-, 16-, and 32-bit port sizes. However, if the bus cycle is slow enough

(more than 13 clocks), performance will be degraded.

Loading...

Loading...