MPC823e Instruction Set

MOTOROLA

MPC823e REFERENCE MANUAL

B-5

INSTRUCTION SET

B

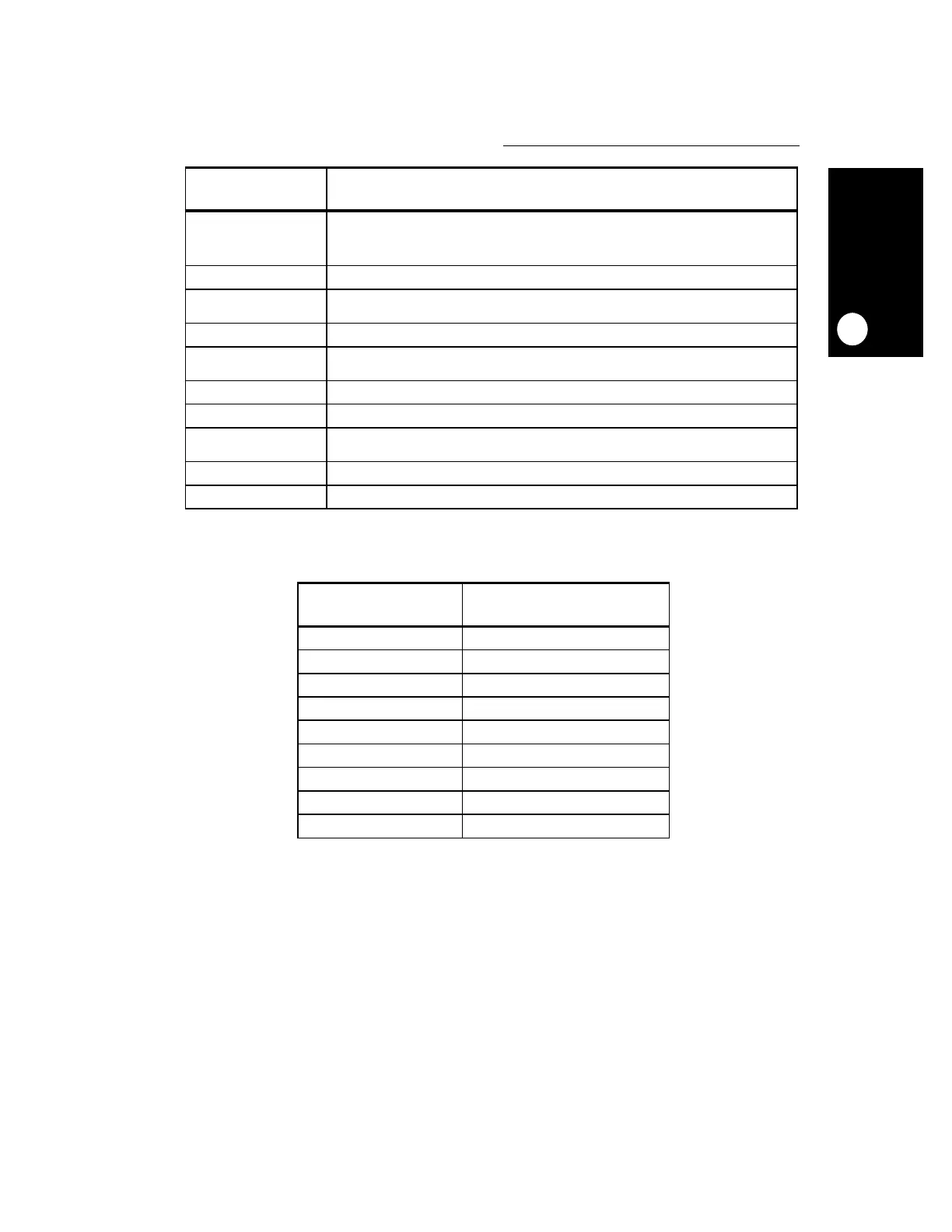

The table below describes instruction field notation conventions used in this appendix.

NIA Next instruction address, which is the 32-bit address of the next instruction to be executed

(the branch destination) after a successful branch. In pseudocode, a successful branch is

indicated by assigning a value to NIA. For instructions which do not branch, the next

instruction address is CIA + 4. Does not correspond to any architected register.

OEA PowerPC operating environment architecture

Rotate Rotate the contents of a register right or left n bits without masking. This operation is used

for rotate and shift instructions.

Set Bits are set to 1.

Shift Shift the contents of a register right or left n bits, clearing vacated bits (logical shift). This

operation is used for rotate and shift instructions.

SPR(x) Special-purpose register x

TRAP Invoke the system trap handler.

Undefined An undefined value. The value may vary from one implementation to another, and from

one execution to another on the same implementation.

UISA PowerPC user instruction set architecture

VEA PowerPC virtual environment architecture

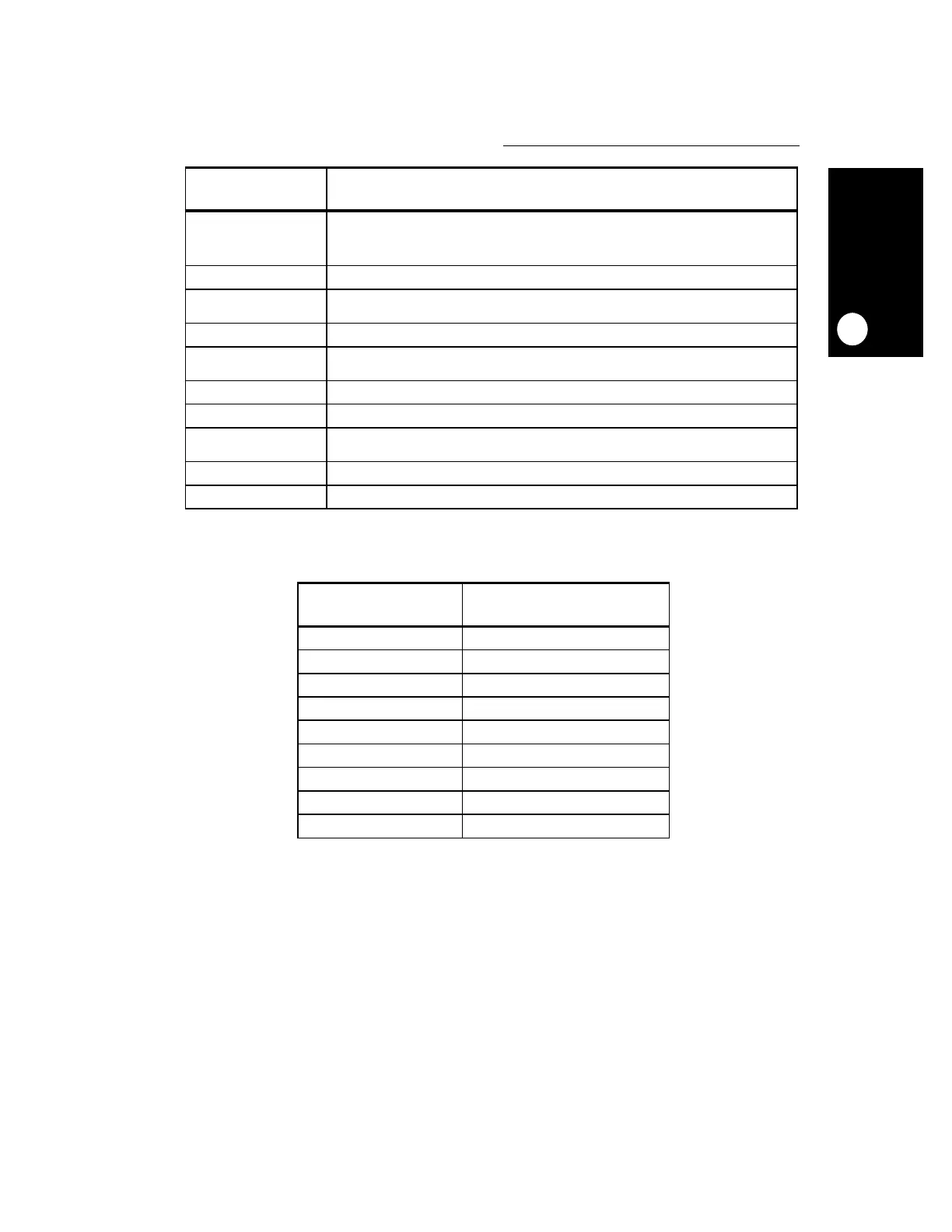

THE ARCHITECTURE

SPECIFICATION

EQUIVALENT

BA, BB, BT

crb

A,

crb

B,

crb

D (respectively)

Dd

DS ds

FXM CRM

RA, RB, RT, RS

r

A,

r

B,

r

D,

r

S (respectively)

SI SIMM

U IMM

UI UIMM

/, //, /// 0...0 (shaded)

NOTATION/

CONVENTION

DEFINITION

Loading...

Loading...