Memory Management Unit

11-8

MPC823e REFERENCE MANUAL

MOTOROLA

MEMORY MANAGEMENT

11

UNIT

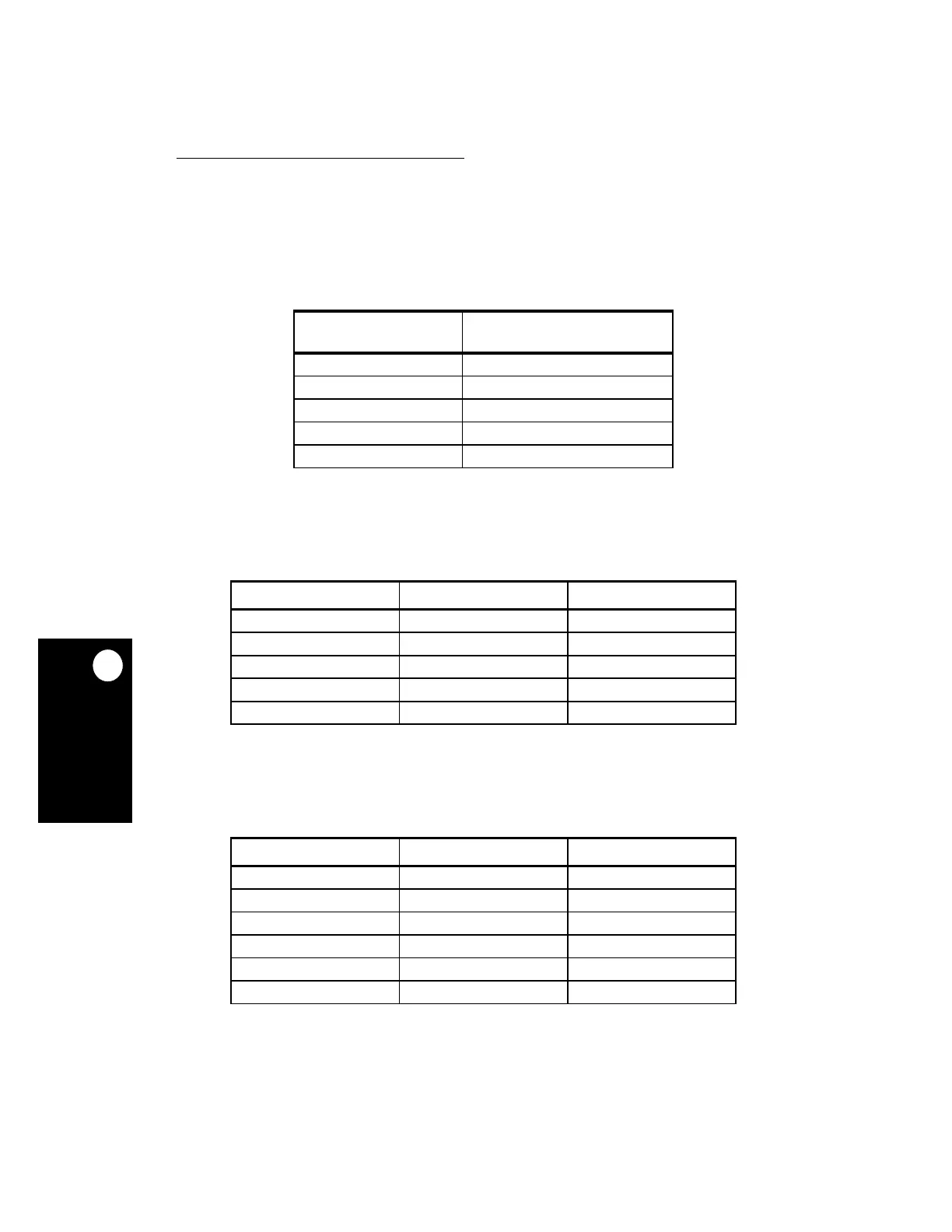

During the memory management unit’s address translation, the most-significant bits of the

missed effective address are replaced by the real page address bits from the level two page

descriptor. The number of replaced bits depends on the page size. The rest of the real

address bits are taken directly from the effective address. See Table 11-1 for details.

Table 11-1. Number of Effective Address Bits Replaced

By Real Address Bits

PAGE SIZE NUMBER OF REPLACED

EFFECTIVE ADDRESS BITS

1K 20

4K 20

16K 18

512K 13

8M 9

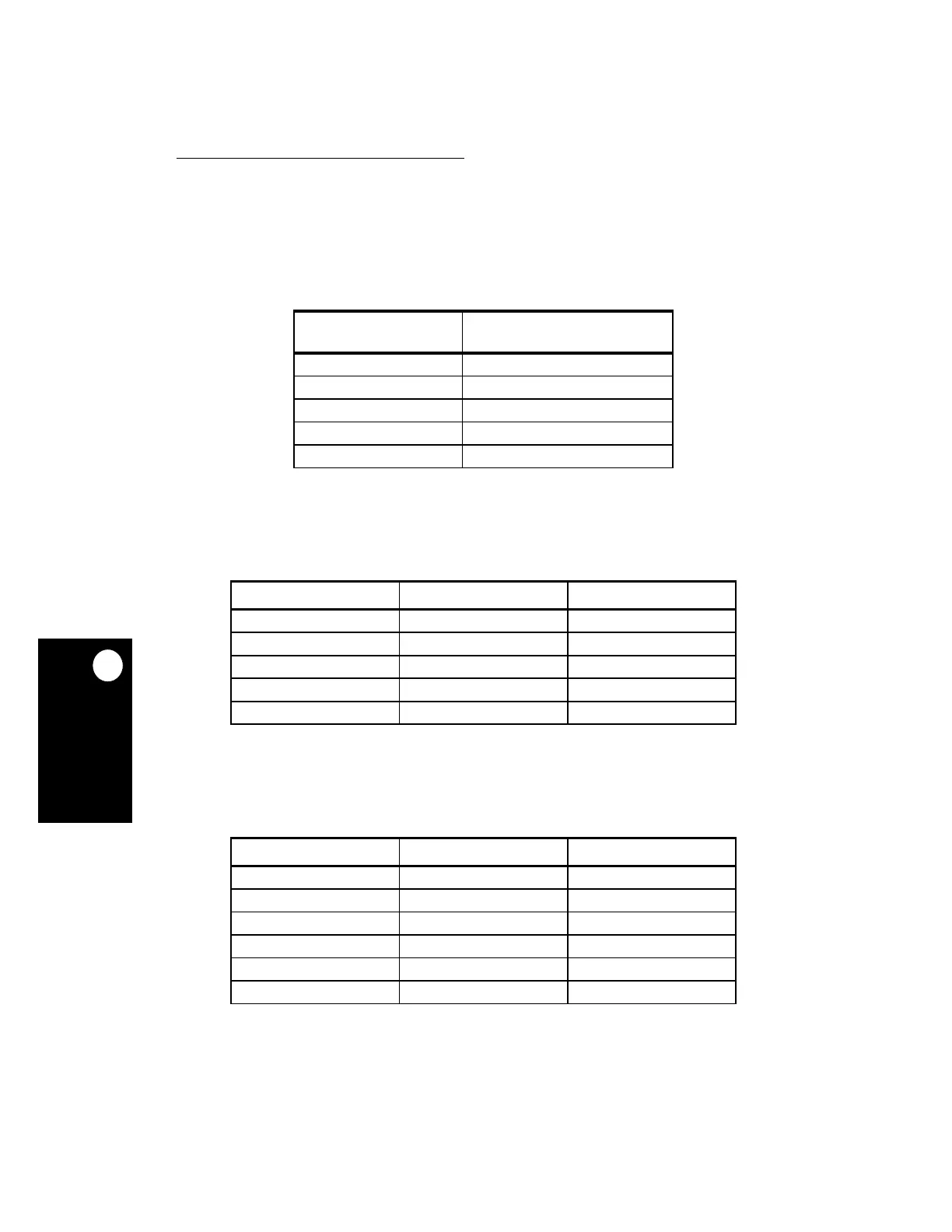

Table 11-2. Number of Identical Entries Required in

the Level One Table

PAGE SIZE MD_CTR

TWAM

= 0 MD_CTR

TWAM

= 1

1K 1 —

4K 1 1

16K 1 1

512K 1 1

8M 8 2

Table 11-3. Number of Identical Entries Required in

the Level Two Table

PAGE SIZE MD_CTR

TWAM

= 0 MD_CTR

TWAM

= 1

1K 1 —

4K 4 1

16K 16 4

512K 512 128

8M 1,024 1,024

Loading...

Loading...