External Bus Interface

MOTOROLA

MPC823e REFERENCE MANUAL

13-5

EXTERNAL BUS

13

INTERFACE

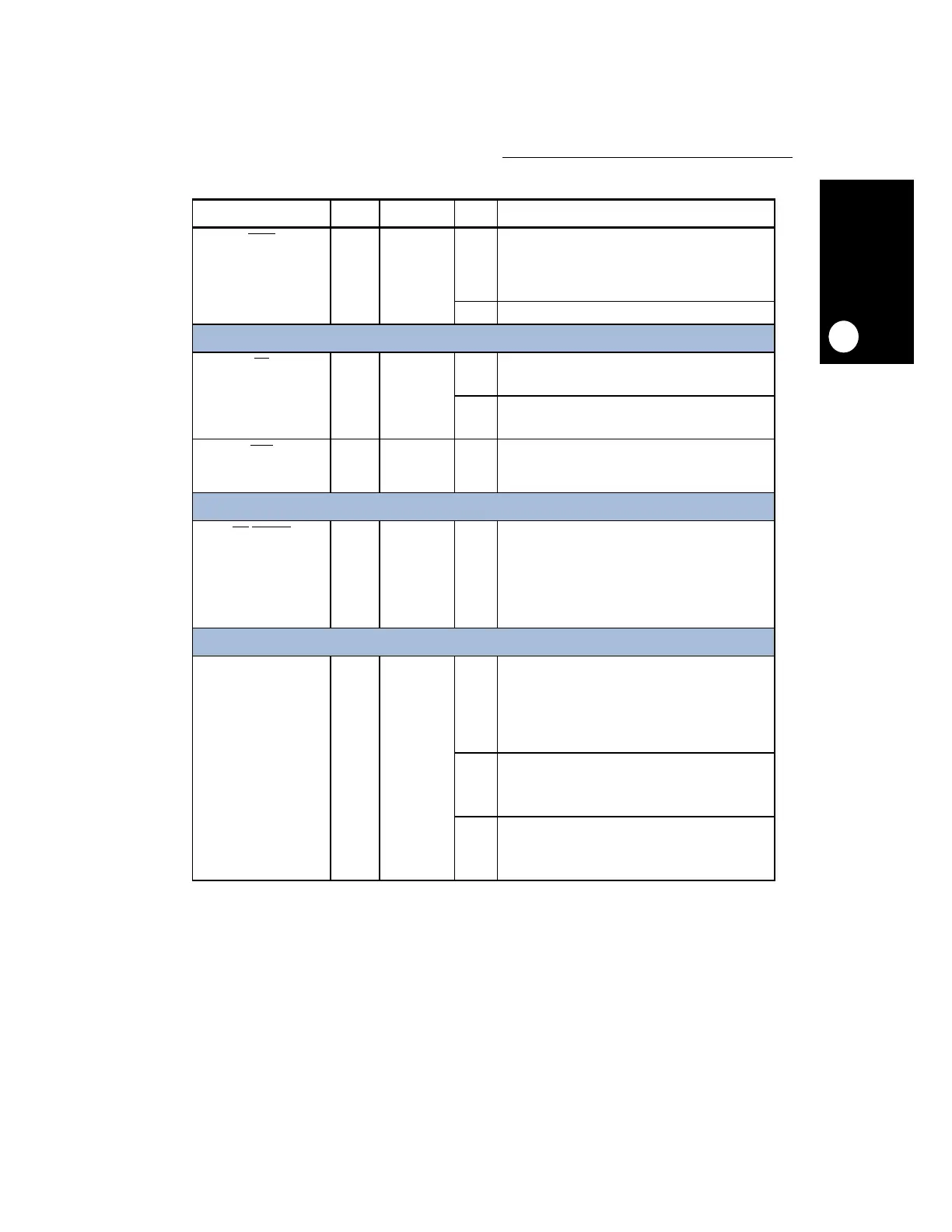

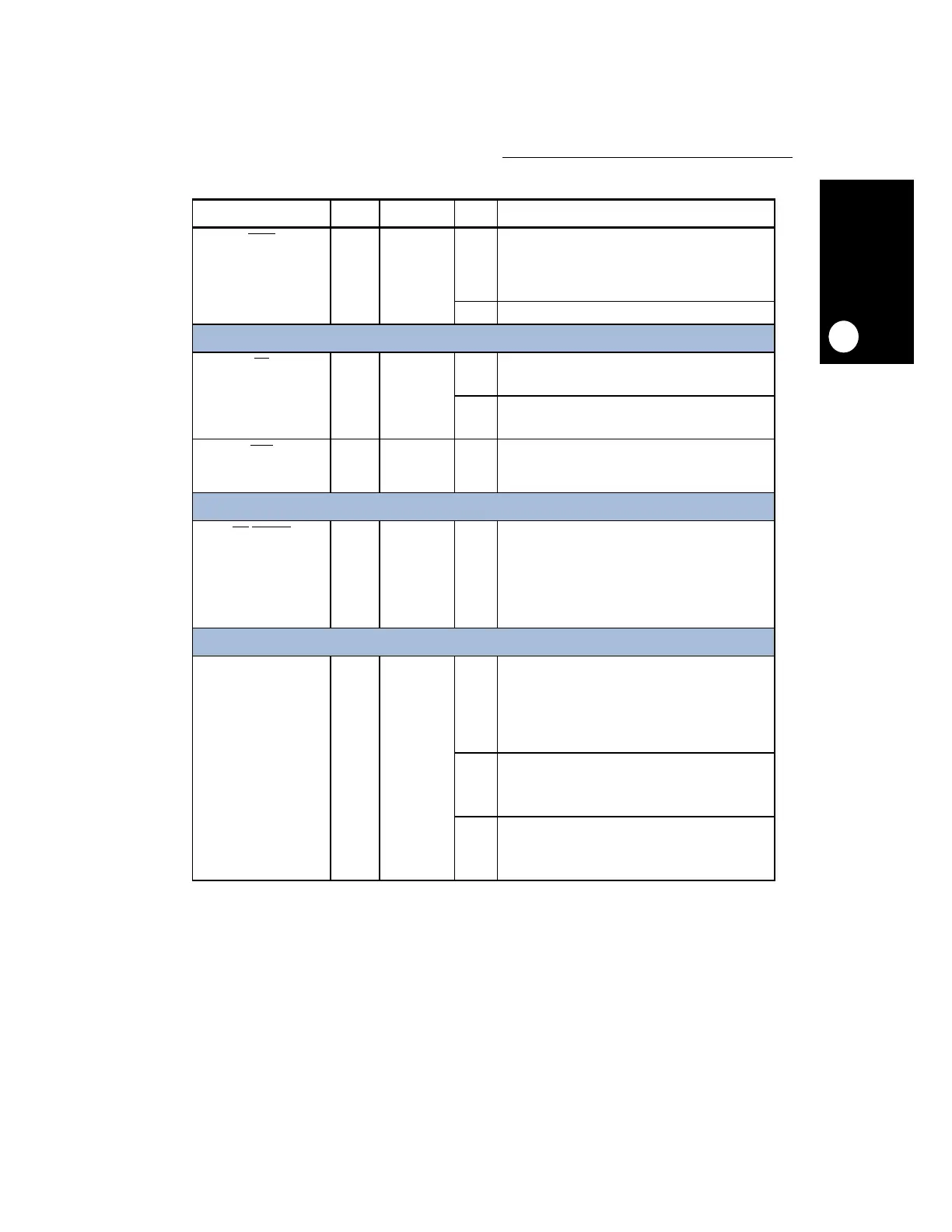

BDIP

1 Low O

Burst Data In Progress

—Driven by the MPC823e

when it owns the external bus. It is part of the burst

protocol. Asserted indicates that the second beat in

front of the current one is requested by the master.

This signal is negated prior to the end of a burst to

terminate the burst data phase early.

I Used only for testing purposes.

TRANSFER START

TS

1 Low O

Transfer Start

—Driven by the MPC823e when it

owns the external bus.It indicates the start of a

transaction on the external bus.

I Sampled by the MPC823e when an external device

initiates a transaction and the memory controller was

configured to handle external master accesses.

STS

1 Low O

Special Transfer Start

—Driven by the MPC823e

when it owns the external bus. It indicates the start of

a transaction on the external bus or an internal

transaction in show cycle mode.

RESERVATION PROTOCOL

KR

/RETRY 1 Low I

Kill Reservation/Retry

—When a bus cycle is

initiated by a

stwcx

instruction that was issued by the

core to a nonlocal bus on which the storage

reservation has been lost, this signal is used by the

nonlocal bus interface to back-off the cycle. Refer to

Section 13.4.10 Storage Reservation Protocol

.

For a regular transaction, this signal is driven by the

slave device to indicate that the MPC823e has to

relinquish ownership of the bus and retry the cycle.

DATA

D[0:31] 32 High I/O

Data Bus

—The data bus has the following byte lane

assignments:

Data Byte Byte Lane

D[0:7] 0

D[8:15] 1

D[16:23] 2

D[24:31] 3

O Driven by the MPC823e when it owns the external bus

and has initiated a write transaction to a slave device.

For single beat transactions, if external A[6:31] and

TSIZ[0:1] do not select the byte lanes for transfer,

they will not supply valid data.

I Driven by the slave in a read transaction. For single

beat transactions, if external A[6:31] and TSIZ[0:1] do

not select the byte lanes for transfer, they will not be

sampled by the MPC823e. It is also sampled by the

MPC823e when the external master acquires the bus.

Table 13-1. Bus Interface Signals (Continued)

MNEMONIC PINS ACTIVE I/O DESCRIPTION

Loading...

Loading...