Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-13

RISC

COMMUNICATION

16

PROCESSOR MODULE

• GCI TIMEOUT—The GCI timeout command causes the MPC823e transmitter to send

an abort request on the E bit of the GCI bus.

• USB—The USB commands have the same opcode. See Section 16.10 Universal

Serial Bus Controller for a more detailed description.

16.2.6.2.1 CPM Command Register Example. To perform a complete reset of the

communication processor module, you must write 0x8001 to the CPCR, which also sets the

RST and FLG bits. After you issue this command, the CPCR returns a value of 0x0000 after

two clocks. To execute an ENTER HUNT MODE command to the SCC2, write 0x0341 to

the CPCR. While this command is executing, the CPCR returns a 0x0341 value and once it

is finished it returns a 0x0340 value, which clears the FLG bit.

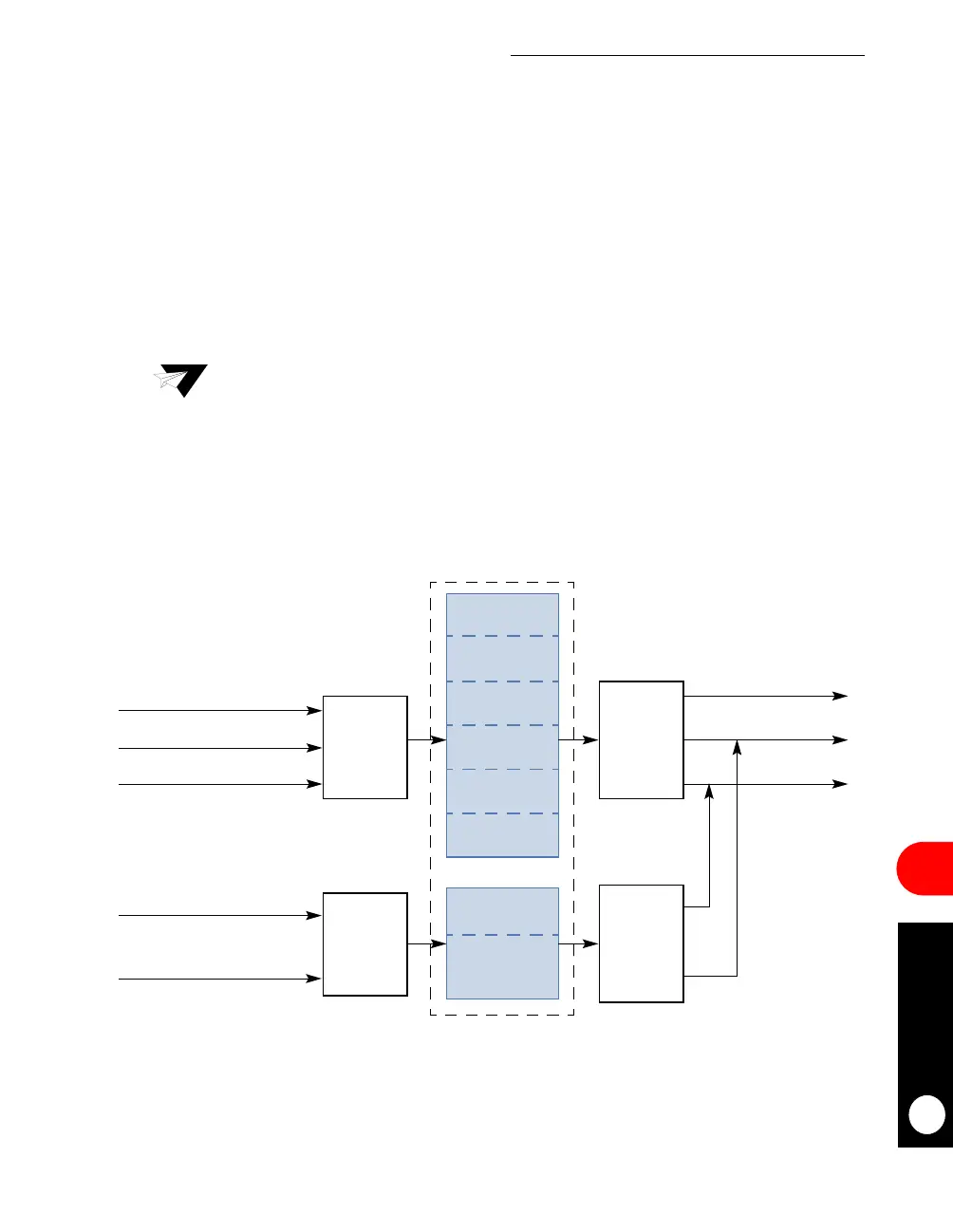

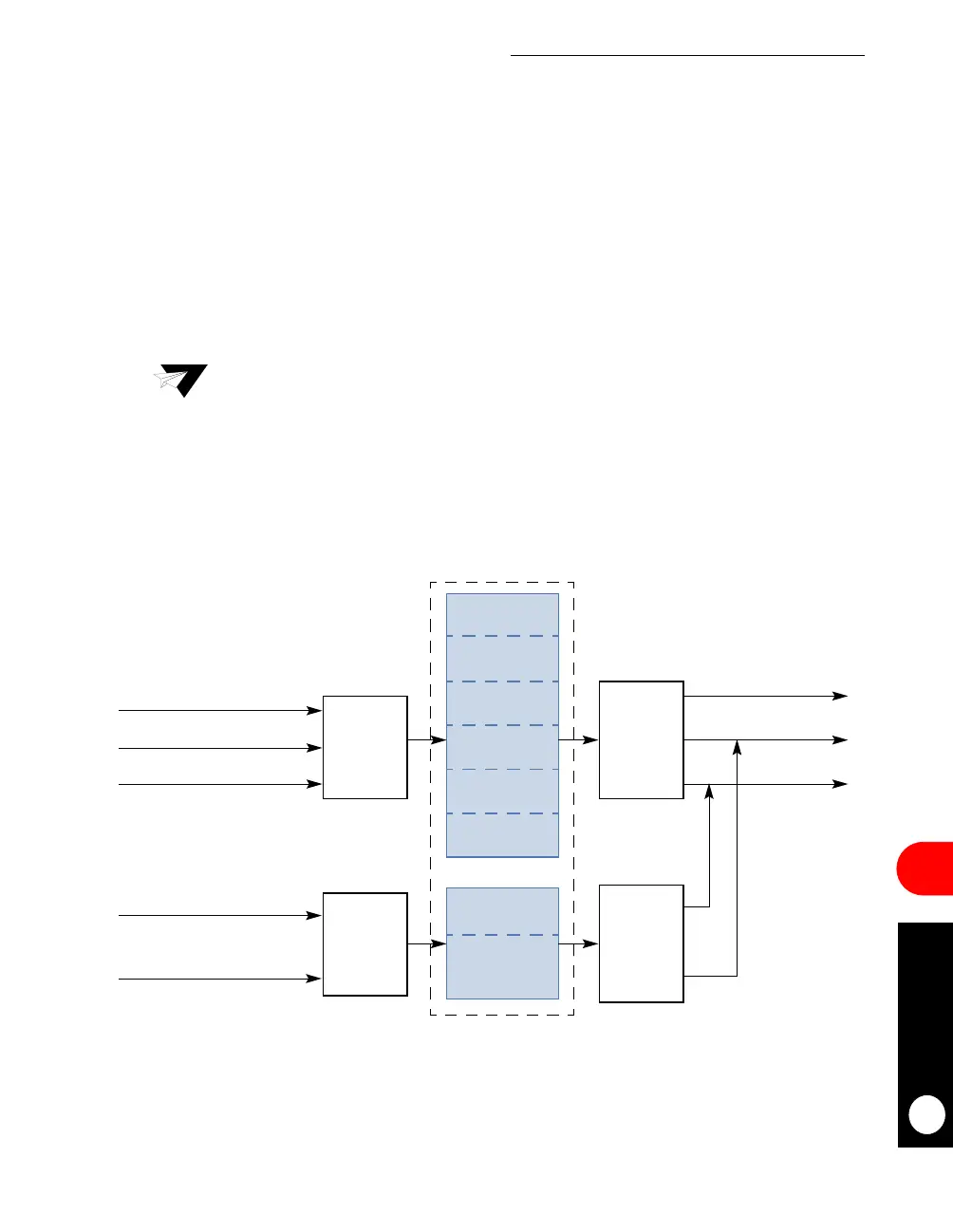

16.2.6.3 DUAL-PORT RAM. The communication processor module has 8,192 bytes of

static RAM that is configured as dual-port memory. A block diagram of the dual-port RAM is

illustrated in Figure 16-4.

Note: The worst-case command execution latency is 120 clocks and the typical

command execution latency is approximately 40 clocks.

Figure 16-4. Dual-Port RAM Block Diagram

1,024 BYTES

512 BYTES

1,024 BYTES

1,024 BYTES

512 BYTES

2,048 BYTES

1,024 BYTES

U BUS ADDRESS

RISC INSTRUCTION ADDRESS

RISC DATA ADDRESS

U BUS ADDRESS

RISC DATA ADDRESS

U-BUS DATA

RISC INSTRUCTION

RISC DATA

DATA

SELECTORS

DUAL-PORT RAM

PARAMETER RAM

ADDRESS

SELECTORS

ADDRESS

SELECTORS

DATA

SELECTORS

NOTE: The shaded area is implemented on the silicon.

1,024 BYTES

Loading...

Loading...