Communication Processor Module

16-110 MPC823e REFERENCEMANUAL MOTOROLA

IDMA

COMMUNICATION

16

PROCESSOR MODULE

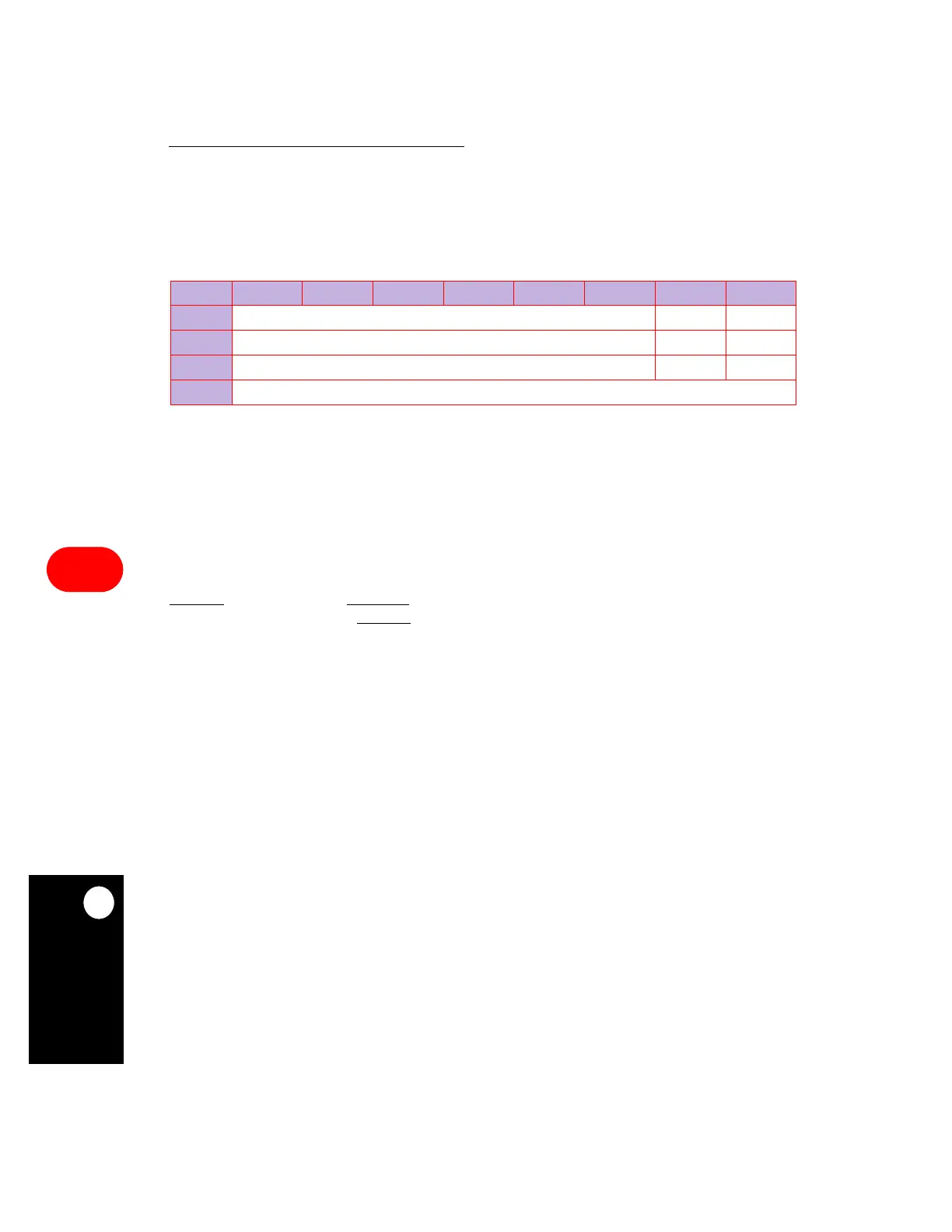

16.6.3.13 IDMA MASK REGISTERS. The 8-bit read/write IDMA1 and 2 mask registers

(IDMRx) have the same bit format as the IDMAx status registers. If a bit in the IDMRx is a

one, the corresponding interrupt in the IDSRx will be enabled. If an IDMRx bit is zero, the

corresponding interrupt in the IDSRx will be masked.

Bits 0–5 and 7—Reserved

These bits are reserved and must be set to 0.

DONE—IDMA Transfer Done

This bit indicates when the IDMA channel terminates a transfer. It is set after servicing a

buffer descriptor that has the L bit set.

16.6.3.14 SINGLE-BUFFER TIMING. A typical single-address burst timing when the IDMA

is in single-buffer mode is illustrated in Figure 16-42. The peripheral device asserts the

DREQ1

pin and waits for SDACK1 to initiate a burst transfer to or from memory. The

peripheral must negate the DREQ1

pin before the last beat of the transfer. Otherwise, IDMA

will assume that another DMA request is pending and will start another burst cycle right after

the completion of the current transfer.

IDMR1 AND IDMR2

BIT 0 1 2 3 4 5 6 7

FIELD RESERVED DONE RESERVED

RESET 000

R/W R/W R/W R/W

ADDR (IMMR & 0xFFFF0000) + 0x914 (IDMR1), 0x91C (IDMR2)

Loading...

Loading...