Communication Processor Module

16-258 MPC823e REFERENCE MANUAL MOTOROLA

COMMUNICATION

16

SCCs

The HDLC bus does not use the echo bit, but rather a separate pin to monitor the data that

is transmitted. The transmitted data is simply connected to the CTSx

input. Second, the

HDLC bus is a synchronous digital open-drain connection for short-distance configurations,

rather than the more complex configurations of an S/T interface. Third, the HDLC bus allows

any HDLC-based frame protocol to be implemented at layer 2, not just LAPD. Fourth, the

HDLC bus devices wait either 8 or 10 bit times before transmitting, rather than 7, 8, 9, or 10

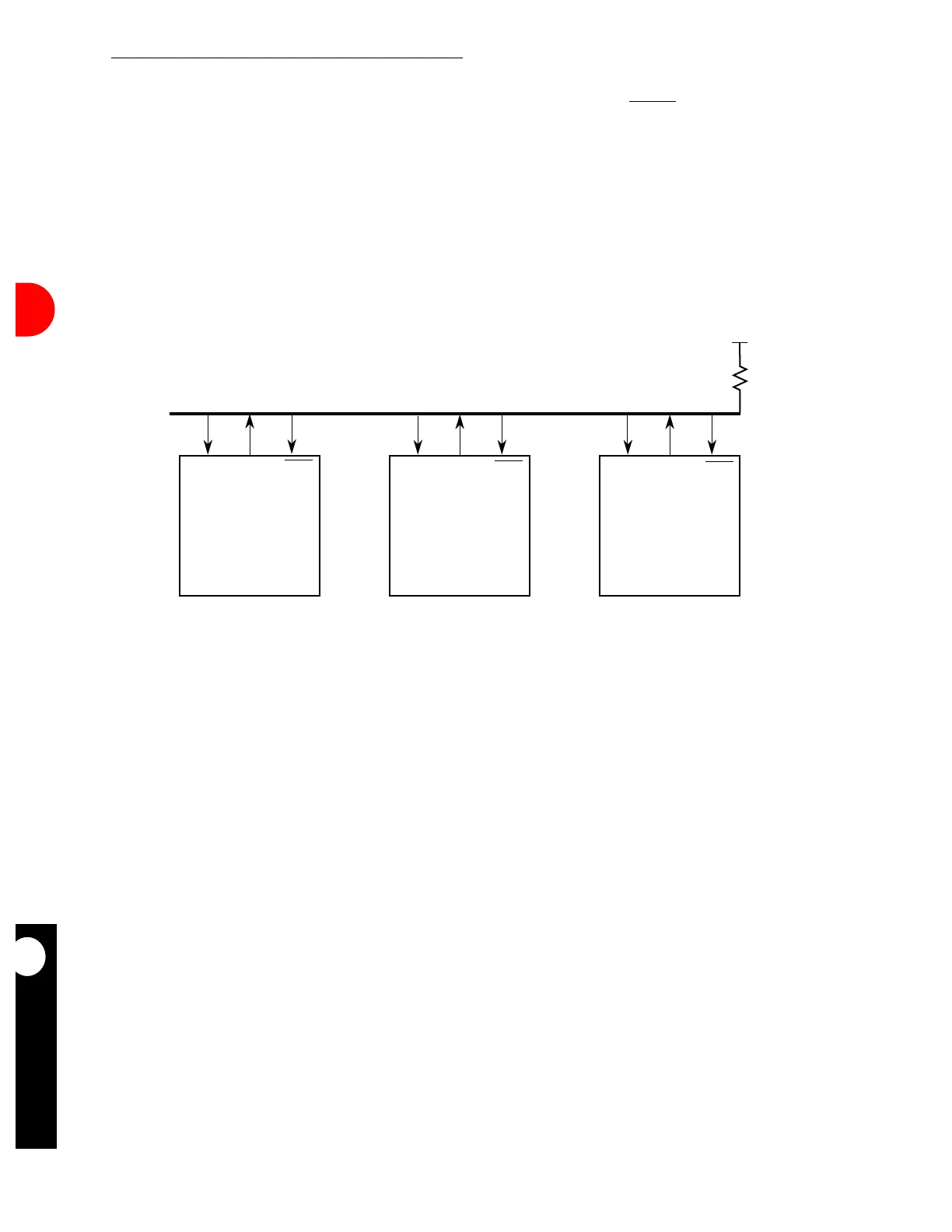

bits. Figure 16-82 illustrates the HDLC bus in its most common LAN configuration, the

multimaster configuration. All stations can transmit and receive data to or from every other

station on the LAN and all transmissions are half-duplex, which is typical in LANs.

Figure 16-82. Typical HDLC Bus Multimaster Configuration

MASTERMASTER

HDLC

CONTROLLER

HDLC BUS LAN

A

HDLC BUS

CONTROLLER

B

HDLC BUS

CONTROLLER

C

MASTER

R

+5

NOTES:

1. Transceivers may be used to extend the LAN size, if necessary.

2. The TXDx pins of slave devices must be configured to open-drain in the port C parallel I/O port.

TXDxRXDx CTSxTXDxRXDx

TXDxRXDx

CTSx

CTSx

Loading...

Loading...