Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-261

COMMUNICATION

16

SCCs

To ensure that all stations gain an equal share of the bus, a priority mechanism is

implemented on the HDLC bus. Once an HDLC bus node has finished transmitting a frame,

it waits 10 consecutive one bits, instead of eight, before beginning the next transmission.

Using this method, all nodes that need to transmit can obtain the bus before a node

transmits twice. Once a node detects that 10 consecutive ones have occurred on the bus, it

tries to transmit and reinstate its original priority of waiting for eight ones.

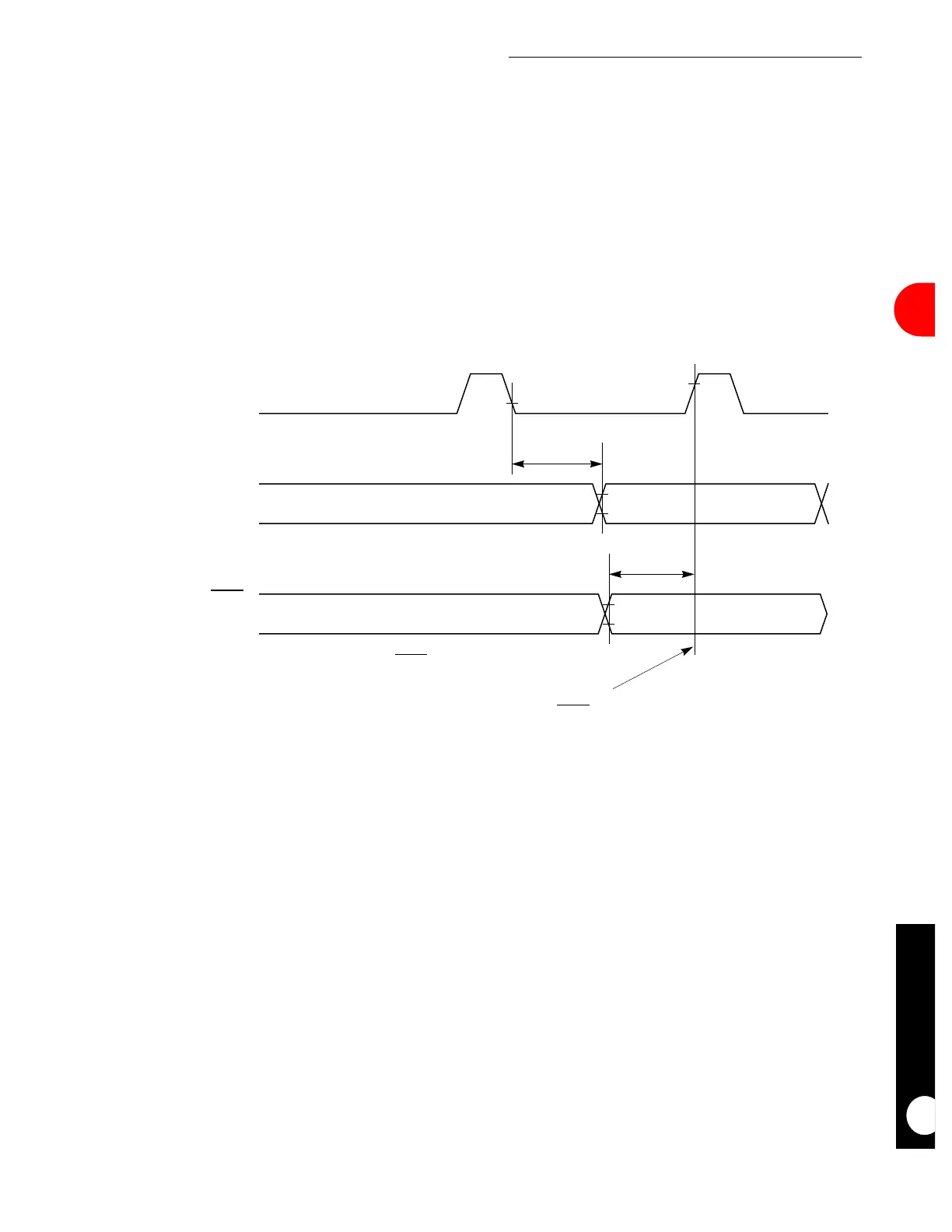

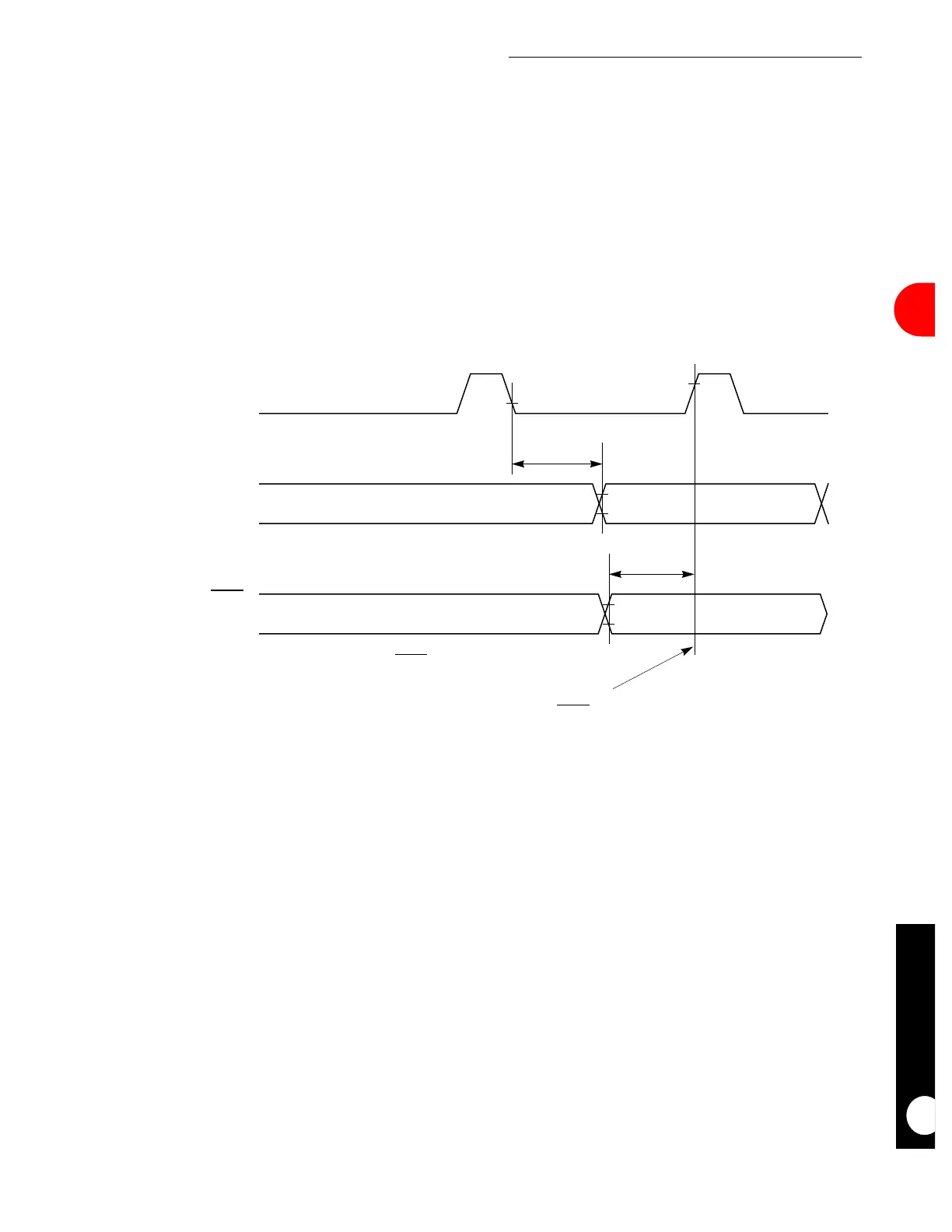

16.9.17.2.1 Improving Performance. Since the HDLC bus is used in a wired-OR

configuration, the limitations of the HDLC bus is determined by the rise time of the one bit.

Figure 16-85 illustrates a method to increase performance. You must supply a clock that is

lower more than it is high, which allows the one bit to have more rise time.

Figure 16-85. Example of a Nonsymmetrical Duty Cycle

TCLK

CTSx

(Input)

TXDx

(Output)

CTSx

sampled at three quarter point.

Collision detected when

TXDx=1, but CTSx

=0.

Loading...

Loading...