Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-337

COMMUNICATION

16

PROCESSOR MODULE

SCCs

• Non-Octet Error (Dribbling Bits)

—

The SCCx Ethernet controller handles up to seven

dribbling bits when the receive frame terminates nonoctet aligned and it checks the

CRC of the frame on the last octet boundary. If there is a CRC error, then the frame

nonoctet aligned error is reported, the RXF bit is set, and the alignment error counter is

incremented. If there is no CRC error, then no error is reported.

• CRC Error—When a CRC error occurs, the channel closes the buffer, sets the CR bit

in the RX buffer descriptor, and the RXF bit in the SCCE–Ethernet register. The channel

also increments the CRC error counter (CRCEC). After receiving a frame with a CRC

error, the receiver enters hunt mode. CRC checking cannot be disabled, but the CRC

error can be ignored if checking is not required.

16.9.23 Programming the SCCx Ethernet Controller

16.9.23.1 SCCx ETHERNET MODE REGISTER. When a serial communication controller

is in Ethernet mode, the 16-bit, memory-mapped, read/write protocol-specific mode register

is referred to as the SCCx Ethernet mode register (PSMR–SCC Ethernet). Since each

protocol has specific requirements, the PSMR bits are different for each implementation.

HBC—Heartbeat Checking

0 = No heartbeat checking is performed. Do not wait for a collision after transmission.

1 = Wait 20 transmit clocks or 2µs for a collision asserted by the transceiver after

transmission. The HB bit in the TX buffer descriptor is set if the heartbeat is not

heard within 20 transmit clocks.

FC—Force Collision

0 = Normal operation.

1 = The channel forces a collision when each frame is transmitted. The MPC823e must

be configured in loopback operation when using this feature so that you can test

the collision logic. In the end, the retry limit for each transmit frame is exceeded.

RSH—Receive Short Frames

0 = Discard short frames that are not as long as MINFLR.

1 = Receive short frames.

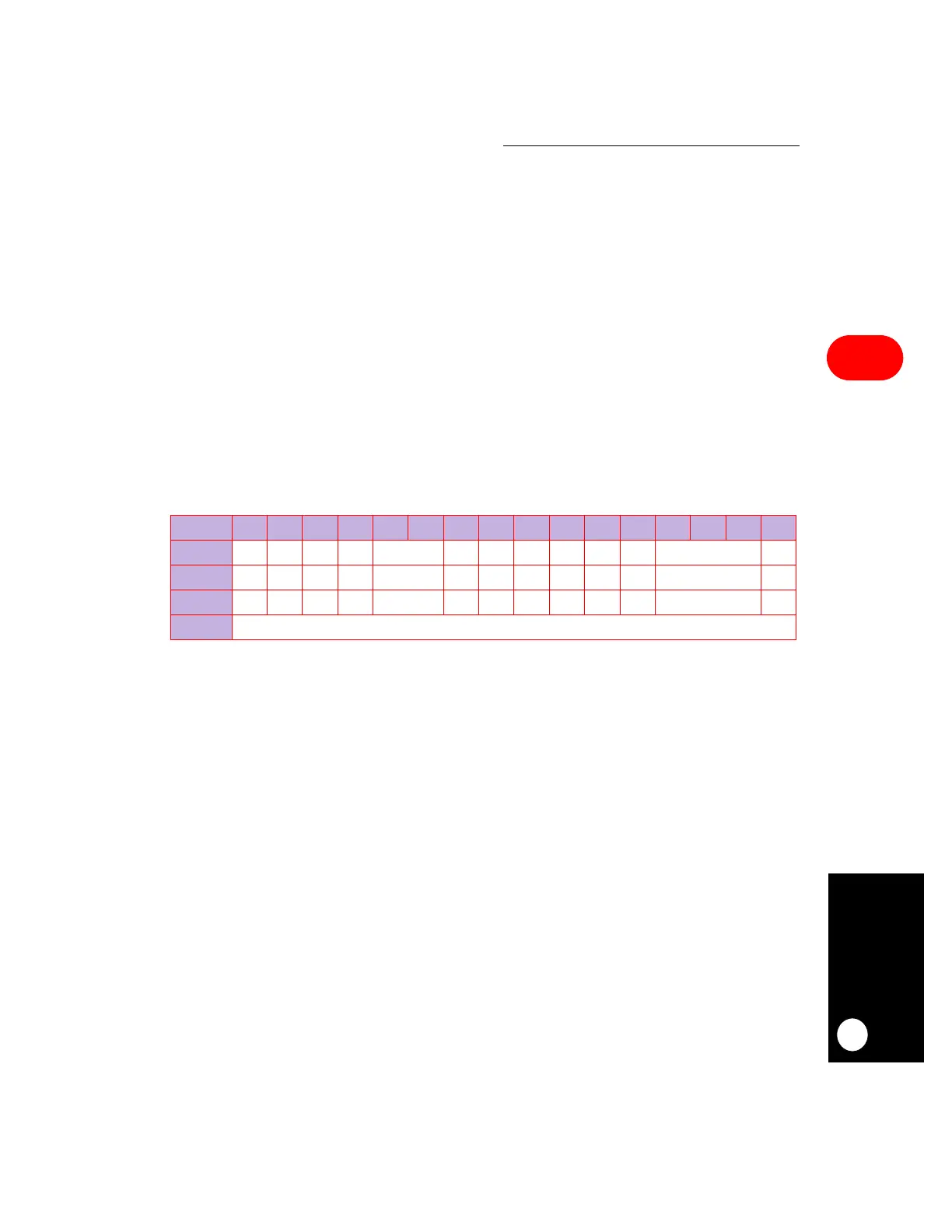

PSMR–SCC ETHERNET

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD HBC FC RSH IAM CRC PRO BRO SBT LPB RES LCW NIB FDE

RESET 0000 0 000000 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR (IMMR & 0xFFFF0000) + 0xA28

Loading...

Loading...