Communication Processor Module

16-376 MPC823e REFERENCE MANUAL MOTOROLA

USB

COMMUNICATION

16

PROCESSOR MODULE

16.10.8.8 USB EVENT REGISTER. The 16-bit, memory-mapped USB event register

(USBER) is used to generate interrupt events and report events recognized by the USB

channel. When an event is recognized, the USB sets the corresponding bit in the USBER.

Interrupts generated by this register may be masked in the USB mask register. A bit is

cleared by writing a one (writing a zero has no effect) and more than one bit can be cleared

at a time. All unmasked bits must be cleared before the communication processor module

will clear the internal interrupt request.

Bits 0–5—Reserved

These bits are reserved and must be set to 0.

RESET—Reset Condition Detected

This bit indicates that the USB reset condition has been asserted.

IDLE—IDLE Status Changed

This bit indicates that a change in the status of the serial line was detected. The real time

idle status is reflected in the USB status register.

TXEx—TX Error 0–3

This bit indicates that an error occurred during transmission for endpoint x (packet not

acknowledged (function), NAK/STALL handshake received (host) or transmit underrun).

SOF—Start of Frame

This bit indicates that a start-of-frame packet was received. The packet is stored in the

FRAME_N parameter RAM entry.

BSY—Busy Condition

This bit indicates that received data has been discarded due to a lack of buffers. This bit is

set after the first character with no receive buffer is received.

TXB—TX Buffer

This bit indicates that a buffer has been transmitted. It is set once the transmit data of the

last character in the buffer was written to the transmit FIFO (the L bit in the TX buffer

descriptor is set to 0) or after the last character was transmitted on the line ( L is set to 1).

RXB—RX Buffer

This bit indicates that a buffer has been received. It is set after the last character has been

written to the receive buffer and the RX buffer descriptor is closed.

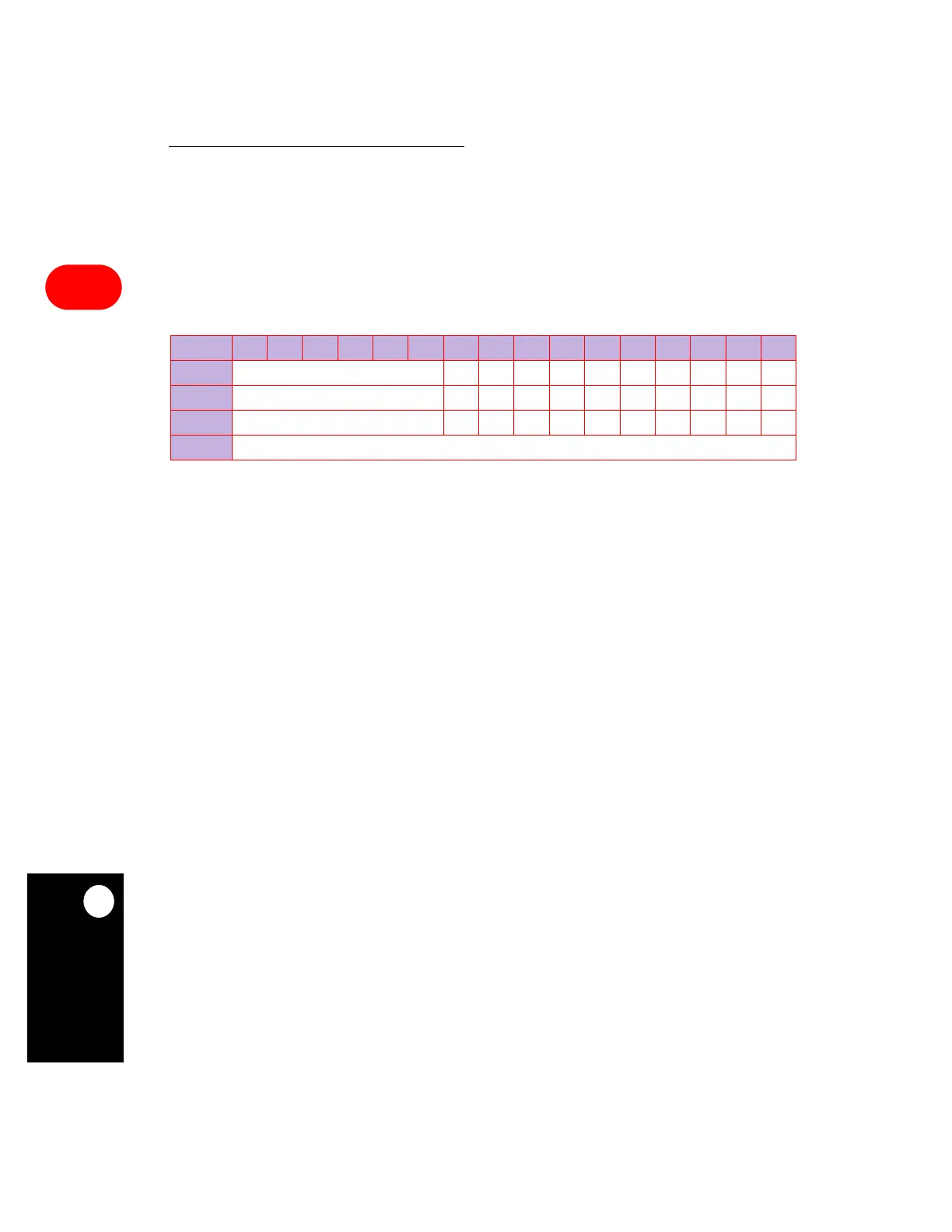

USBER

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

RESERVED RESET IDLE TXE3 TXE2 TXE1 TXE0 SOF BSY TXB RXB

RESET

0 0000000000

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0

x

FFFF0000) + 0

x

A10

Loading...

Loading...