Communication Processor Module

16-394 MPC823e REFERENCE MANUAL MOTOROLA

SMC

COMMUNICATION

16

PROCESSOR MODULE

When the buffer descriptor data is completely written to the transmit FIFO, the SMCx UART

controller writes the message status bits into the buffer descriptor and clears the R bit. An

interrupt is issued if the I bit in the buffer descriptor is set. If the next TX buffer descriptor is

ready, the data from its data buffer is appended to the previous data and transmitted out on

the transmit pin, without any gaps between the buffers. If the next TX buffer descriptor is not

ready, the SMCx UART controller starts transmitting idles and waits for the next TX buffer

descriptor to be ready.

By appropriately setting the I bit in each buffer descriptor, interrupts can be generated after

the transmission of each buffer, a specific buffer, or each block. The SMCx UART controller

then proceeds to the next buffer descriptor in the table. If the CM bit is set in the TX buffer

descriptor, the R bit is not cleared, allowing the associated data buffer to be automatically

retransmitted next time the communication processor module accesses this data buffer. For

instance, if a single TX buffer descriptor is initialized with the CM and W bits set, the data

buffer is continuously transmitted until you clear the R bit of the buffer descriptor.

16.11.6.3 SMCx UART CHANNEL RECEPTION PROCESS. When the core enables the

SMCx receiver in UART mode, it enters hunt mode and waits for the first character to arrive.

Once the first character arrives, the communication processor module checks the first

receive buffer descriptor to see if it is empty and then starts storing characters in the

associated data buffer.

When the data buffer is filled or the MAX_IDL timer expires (if it is enabled) the SMCx UART

controller clears the E bit in the buffer descriptor and generates an interrupt if the I bit in the

buffer descriptor is set. If the incoming data exceeds the length of the data buffer, the SMCx

UART controller fetches the next buffer descriptor in the table and, if it is empty, continues

transferring data to the associated data buffer. If the CM bit is set in the receive buffer

descriptor, the E bit is not cleared, which allows the associated data buffer to be

automatically overwritten next time the communication processor module accesses this

data buffer.

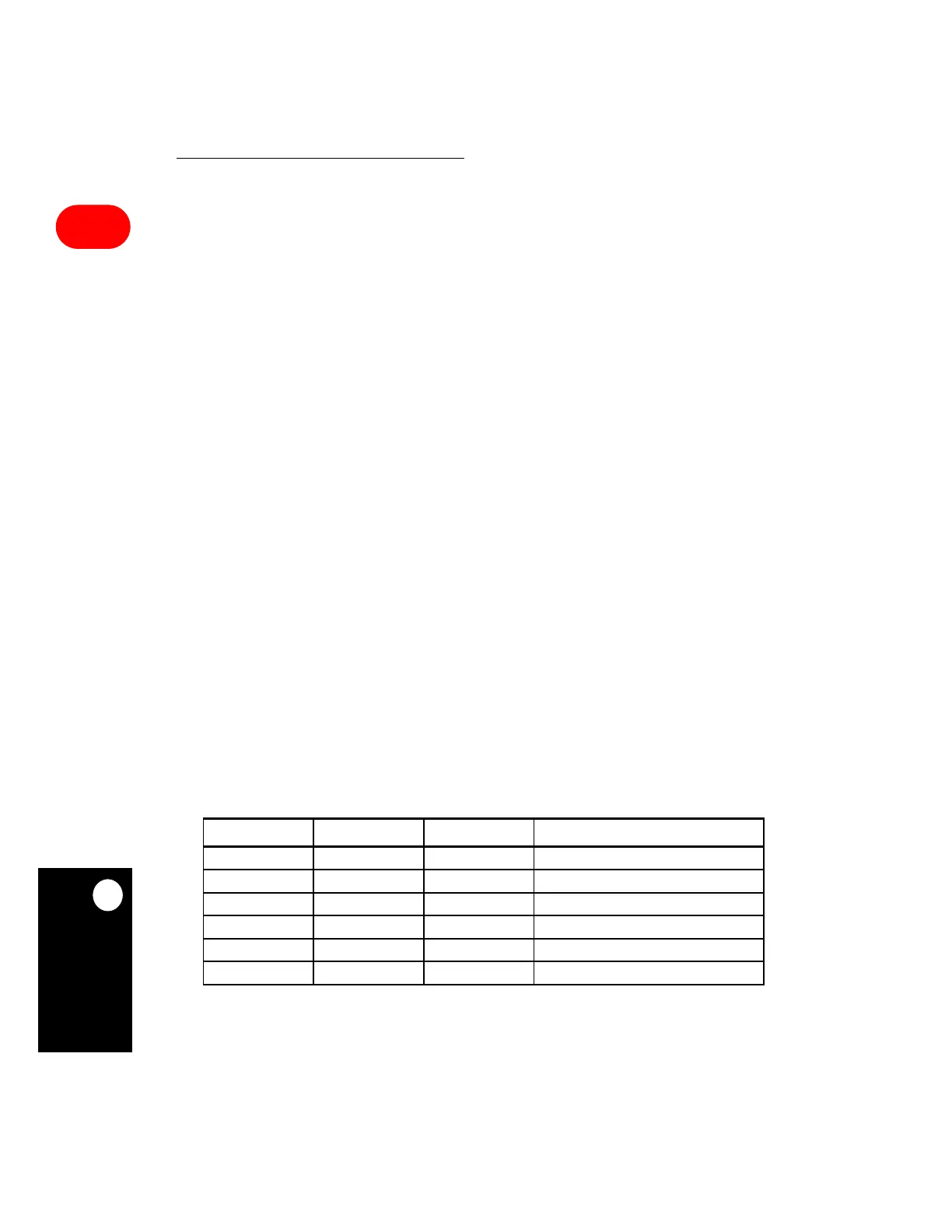

16.11.6.4 SMCx UART PARAMETER RAM MEMORY MAP. When a serial management

controller is configured to operate in UART mode, the SMCx UART controller overlays the

structure used in Table 16-36 with the parameters described in Table 16-37.

Table 16-37. SMCx UART Parameter RAM Memory Map

ADDRESS NAME WIDTH DESCRIPTION

SMCx Base + 28 MAX_IDL Half-word Maximum Idle Characters

SMCx Base + 2A IDLC Half-word Temporary Idle Counter

SMCx Base + 2C BRKLN Half-word Last Received Break Length

SMCx Base + 2E BRKEC Half-word Receive Break Condition Counter

SMCx Base +30 BRKCR Half-word Break Count Register (Transmit)

SMCx Base +32 R_MASK Half-word Temporary Bit Mask

NOTE:

You are only responsible for initializing the items in bold.

SMCx Base = (IMMR & 0xFFFF0000) + 0x3E80 (SMC1) and 0x3F80 (SMC2).

Loading...

Loading...