Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-405

SMC

COMMUNICATION

16

PROCESSOR MODULE

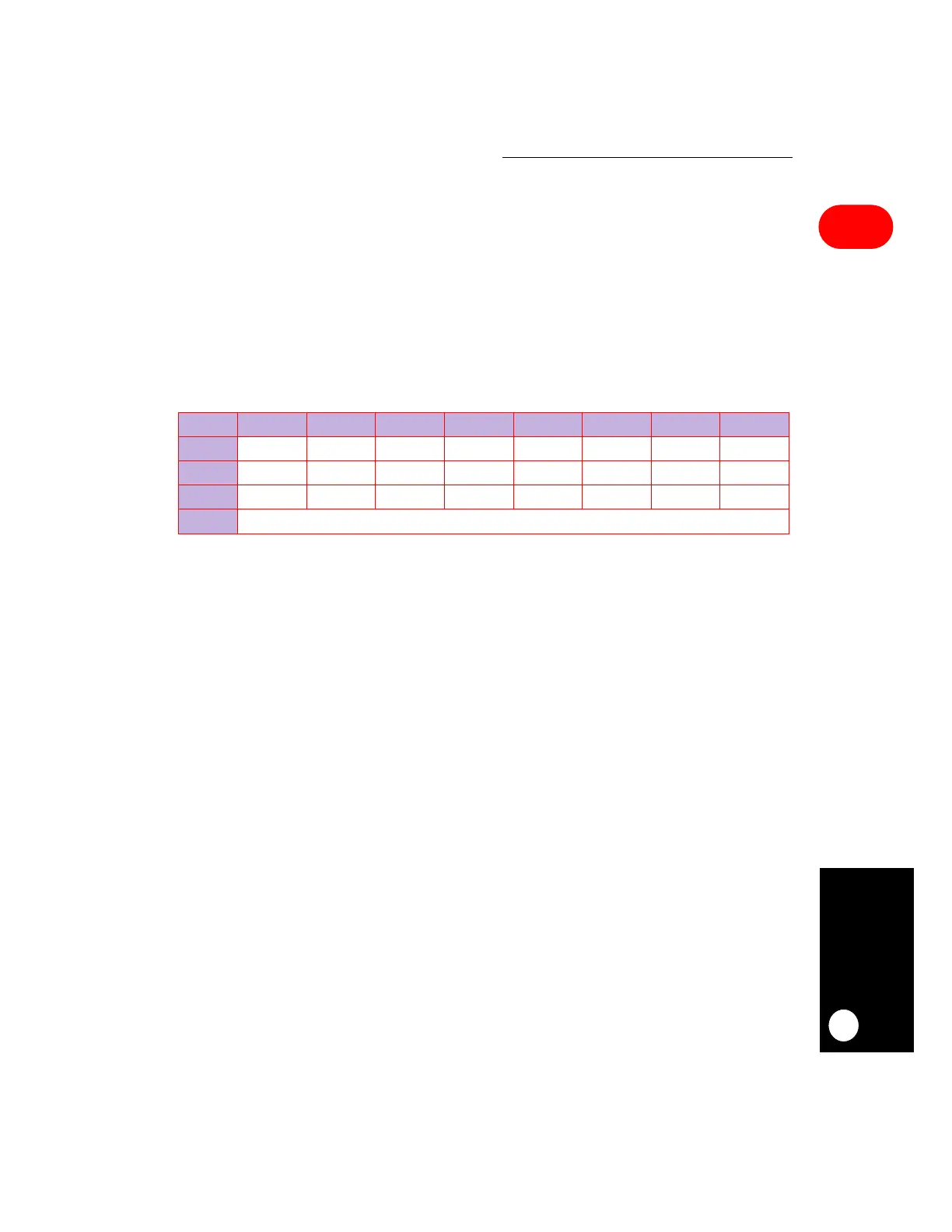

16.11.6.13 SMCx UART EVENT REGISTER. When a serial management controller is in

UART mode, the 8-bit memory-mapped SMCx event register is referred to as the SMCx

UART event (SMCE–UART) register. It is used to generate interrupts and report events

recognized by the SMCx UART channel. When an event is recognized, the SMCx UART

controller sets the corresponding bit in this register.

A bit is cleared by writing a 1 (writing a zero has no effect) and more than one bit can be

cleared at a time. All unmasked bits must be cleared before the communication processor

module clears the internal interrupt request. This register is cleared by reset and can be read

at any time. An example of the timing of various events in the SMCE–UART register is

illustrated in Figure 16-119.

Bit 0, 2, and 4—Reserved

These bits are reserved and must be set to 0.

BRKE—Break End

This bit indicates that an end of break sequence has been detected. It occurs after one idle

bit is received after a break sequence.

BRK—Break Character Received

This bit indicates that a break character has been received. If a very long break sequence

occurs, this interrupt only occurs once after the first all-zeros character is received.

BSY—Busy Condition

This bit indicates that a character has been received and discarded due to a lack of buffers.

It is be set in the middle of the last stop bit of the first receive character for which there is no

available buffer. Reception continues when an empty buffer is provided.

TX—TX Buffer

This bit indicates that a buffer has been transmitted over the SMCx UART channel. It is set

once the transmit data of the last character in the buffer is written to the transmit FIFO. You

must wait two character times to be sure that the data is completely sent over the transmit

pin.

SMCE –UART

BIT 0 1 2 3 4 5 6 7

FIELD RESERVED BRKE RESERVED BRK RESERVED BSY TX RX

RESET 00000000

R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR (IMMR & 0xFFFF0000) + 0xA86 (SMC1), 0xA96 (SMC2)

Loading...

Loading...