Communication Processor Module

16-416 MPC823e REFERENCE MANUAL MOTOROLA

SMC

COMMUNICATION

16

PROCESSOR MODULE

16.11.7.8 SMCx TRANSPARENT CONTROLLER ERRORS. The serial management

controllers report message reception and transmission error conditions using the channel

buffer descriptors and the SMCE–Transparent register. The following transmission errors

can be detected by the SMCx Transparent controller.

• Underrun Error—When this error occurs, the channel stops transmitting the buffer,

closes it, sets the UN bit in the buffer descriptor, sets the TXE bit in the event register

and causes an interrupt if the TXE bit is set in the mask register. The channel resumes

transmission after it receives the RESTART TRANSMIT command. Underrun cannot

occur between frames.

• Overrun Error—A serial management controller maintains an internal FIFO for

receiving data. The communication processor module begins programming the SDMA

channel if the data buffer is in external memory when the first character is received into

the FIFO. If a FIFO overrun occurs, a serial management controller writes the received

data character to the internal FIFO over the previously received character. The previous

character and its status bits are lost. Then the channel closes the buffer, sets the OV

bit in the receive buffer descriptor, and generates the receive interrupt if it is enabled.

Reception then continues as normal.

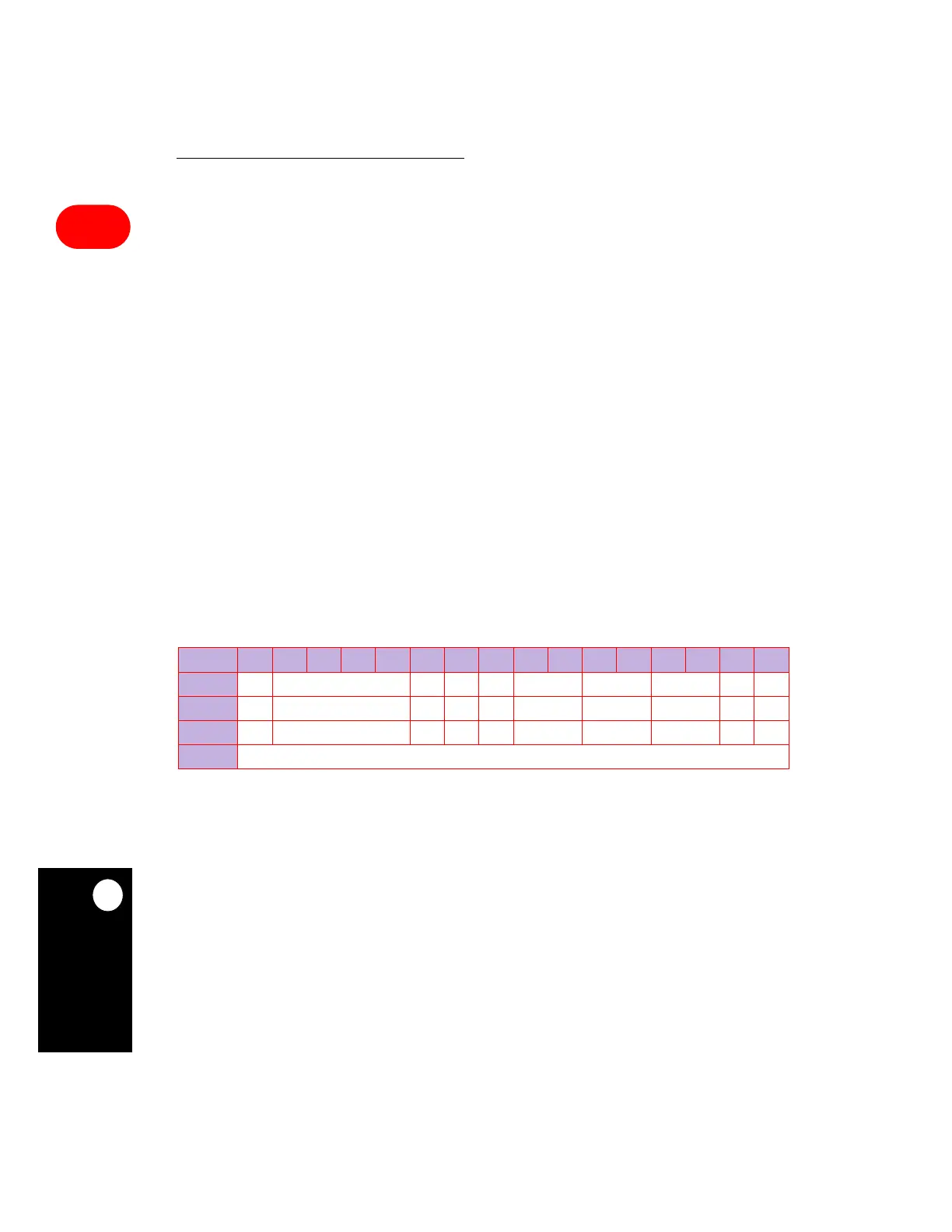

16.11.7.9 SMCx TRANSPARENT MODE REGISTER. When a serial management

controller is in transparent mode, the 16-bit, memory-mapped, read/write SMCx mode

register is referred to as the SMCx transparent mode register (SMCMR–Transparent). The

function of bits 8-15 is common to each SMCx protocol, but bits 0-7 vary according to the

protocol selected by the SM bits of this register.

Bits 0, 5, and 8–9—Reserved

These bits are reserved and must be set to 0.

SMCMR–TRANSPARENT

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

RES CLEN RES BS REVD RESERVED SM DM TEN REN

RESET

0 0 000 0 0 0 00

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0xA82 (SMC1), 0xA92 (SMC2)

Loading...

Loading...