Communication Processor Module

16-434 MPC823e REFERENCE MANUAL MOTOROLA

SPI

COMMUNICATION

16

PROCESSOR MODULE

16.12.1 Features

The following is a list of the serial peripheral interface’s main features:

• Four-Wire Interface (SPIMOSI, SPIMISO, SPICLK, and SPISEL

)

• Full-Duplex Operation

• Works with Data Characters from 4 to 16 Bits Long

• Supports Back-to-Back Character Transmission and Reception

• Master or Slave SPI Modes Supported

• Multimaster Environment Support

• Continuous Transfer Mode for Autoscanning Peripherals

• Supports Maximum Clock Rates of 6.25MHz in Master Mode and 12.5MHz in Slave

Mode, Assuming a 25MHz System Clock is Used

• Independent Programmable Baud Rate Generator

• Programmable Clock Phase and Polarity

• Open-Drain Output Pins Support Multimaster Configuration

• Local Loopback Capability for Testing

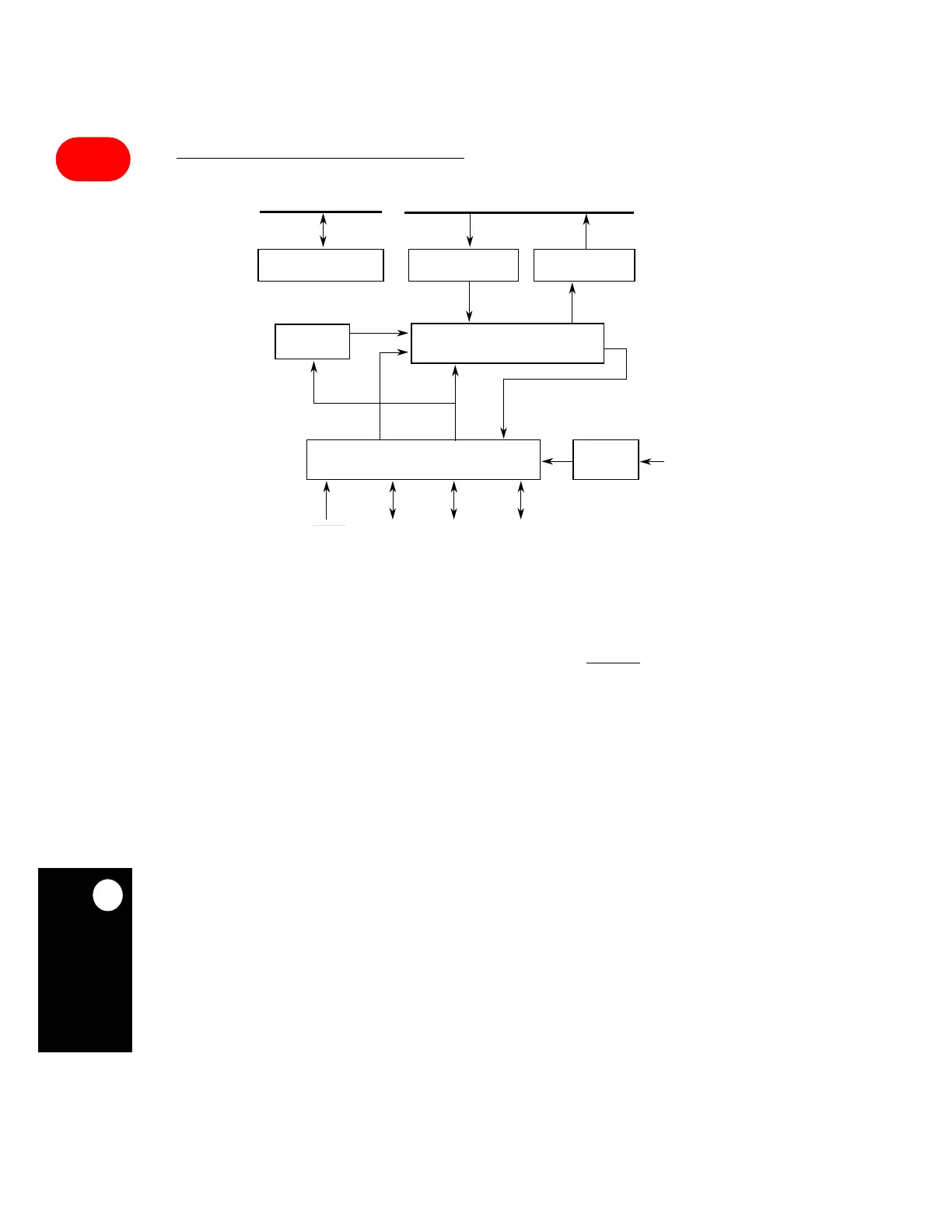

Figure 16-122. SPI Block Diagram

TRANSMIT_REG

RECEIVE_REG

SHIFT_REGISTER

COUNTER

PINS INTERFACE

SPI MODE REG

PERIPHERAL BUSIMB

SPI BRG

SPIMISO

SPIMOSI

SPICLK

IN_CLK

RXD

TXD

BRGCLK

SPISEL

Loading...

Loading...