Communication Processor Module

16-438 MPC823e REFERENCE MANUAL MOTOROLA

SPI

COMMUNICATION

16

PROCESSOR MODULE

16.12.3.2 SPI PARAMETER RAM MEMORY MAP. The SPI parameter RAM area begins

at the SPI base address and is used for the general SPI parameters. Notice that it is similar

to the SCCx general-purpose parameter RAM. You must initialize certain parameter RAM

values before the serial peripheral interface is enabled. The communication processor

module initilizes the other values. Once initialized, the parameter RAM values do not usually

need to be accessed by your software. They only need to be modified when there is no serial

peripheral interface activity in progress.

• RBASE and TBASE—The dual-port RAM starts receiving and transmitting data for the

RX and TX buffer descriptors in the RBASE and TBASE entries. They provide a great

deal of flexibility for partitioning buffer descriptors for a serial peripheral interface. You

must initialize these entries before enabling the corresponding channel. You must not

configure the SPI buffer descriptor tables to overlap with the tables of the USB, SMCx,

and SCCx or erratic operation will occur. RBASE and TBASE must contain a value that

is divisible by eight.

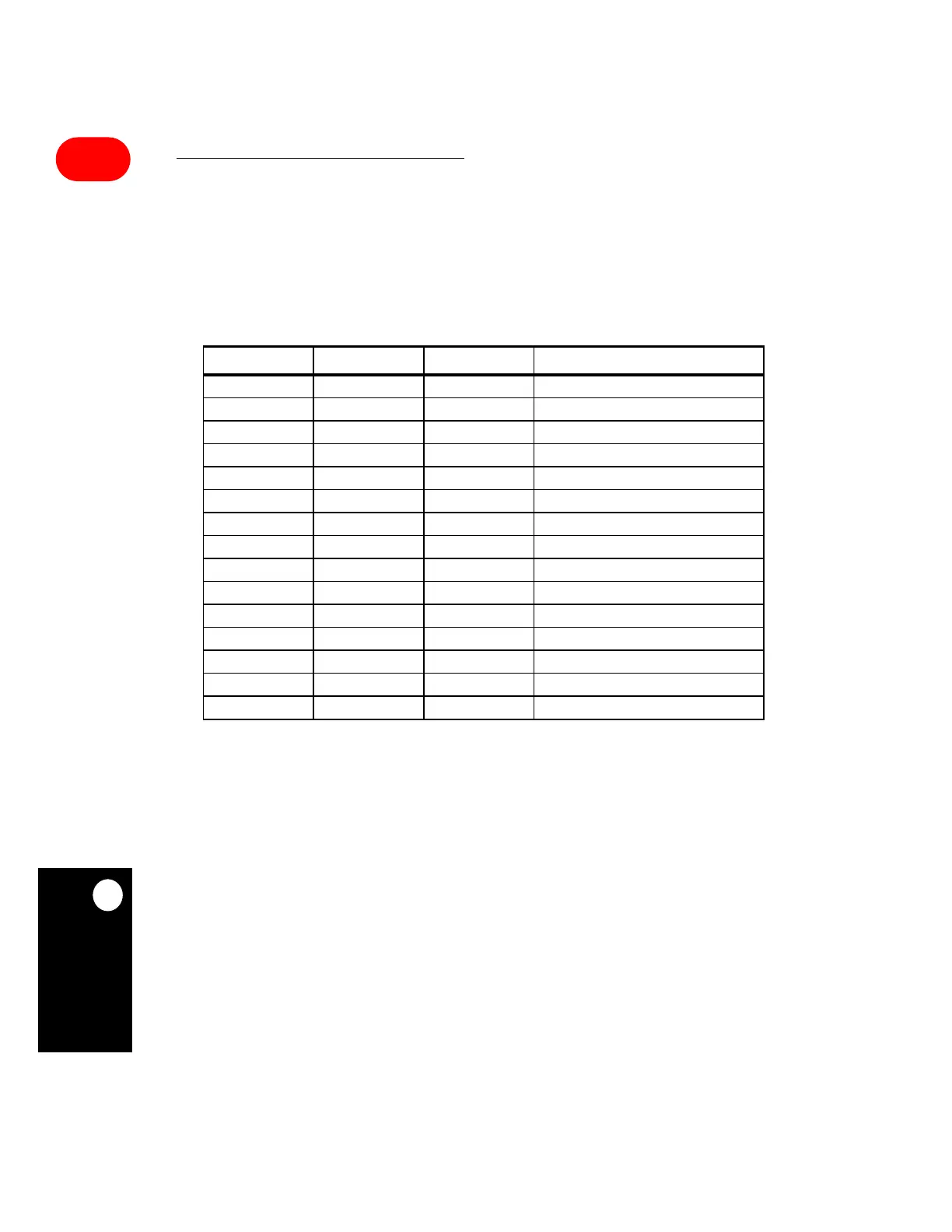

Table 16-39. SPI Parameter RAM Memory Map

ADDRESS NAME WIDTH DESCRIPTION

SPI Base + 00 RBASE Half-word RX Buffer Descriptor Base Address

SPI Base+ 02 TBASE Half-word TX Buffer Descriptor Base Address

SPI Base+ 04 RFCR Byte RX Function Code

SPI Base+ 05 TFCR Byte TX Function Code

SPI Base+ 06 MRBLR Half-word Maximum Receive Buffer Length

SPI Base+ 08 RSTATE Word RX Internal State

SPI Base+ 0C RPTR Word RX Internal Data Pointer

SPI Base + 10 RBPTR Half-word RX Buffer Descriptor Pointer

SPI Base + 12 RCNT Half-word RX Internal Byte Count

SPI Base + 14 RTMP Word RX Temp

SPI Base + 18 TSTATE Word TX Internal State

SPI Base + 1C TPTR Word TX Internal Data Pointer

SPI Base + 20 TBPTR Half-word TX Buffer Descriptor Pointer

SPI Base + 22 TCNT Half-word TX Internal Byte Count

SPI Base + 24 TTMP Word TX Temp

NOTE:

You are only responsible for initializing the items in bold.

SPI Base = (IMMR & 0xFFFF0000) + 0x3D80.

SCCx Ethernet parameter RAM space overlaps the SPI parameter RAM space. The address range

for SCCx space is 0x1000 through 0x1CA3. You need a microcode patch to run SPI and Ethernet

concurrently.

Loading...

Loading...