Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-502

CPIC

COMMUNICATION

16

PROCESSOR MODULE

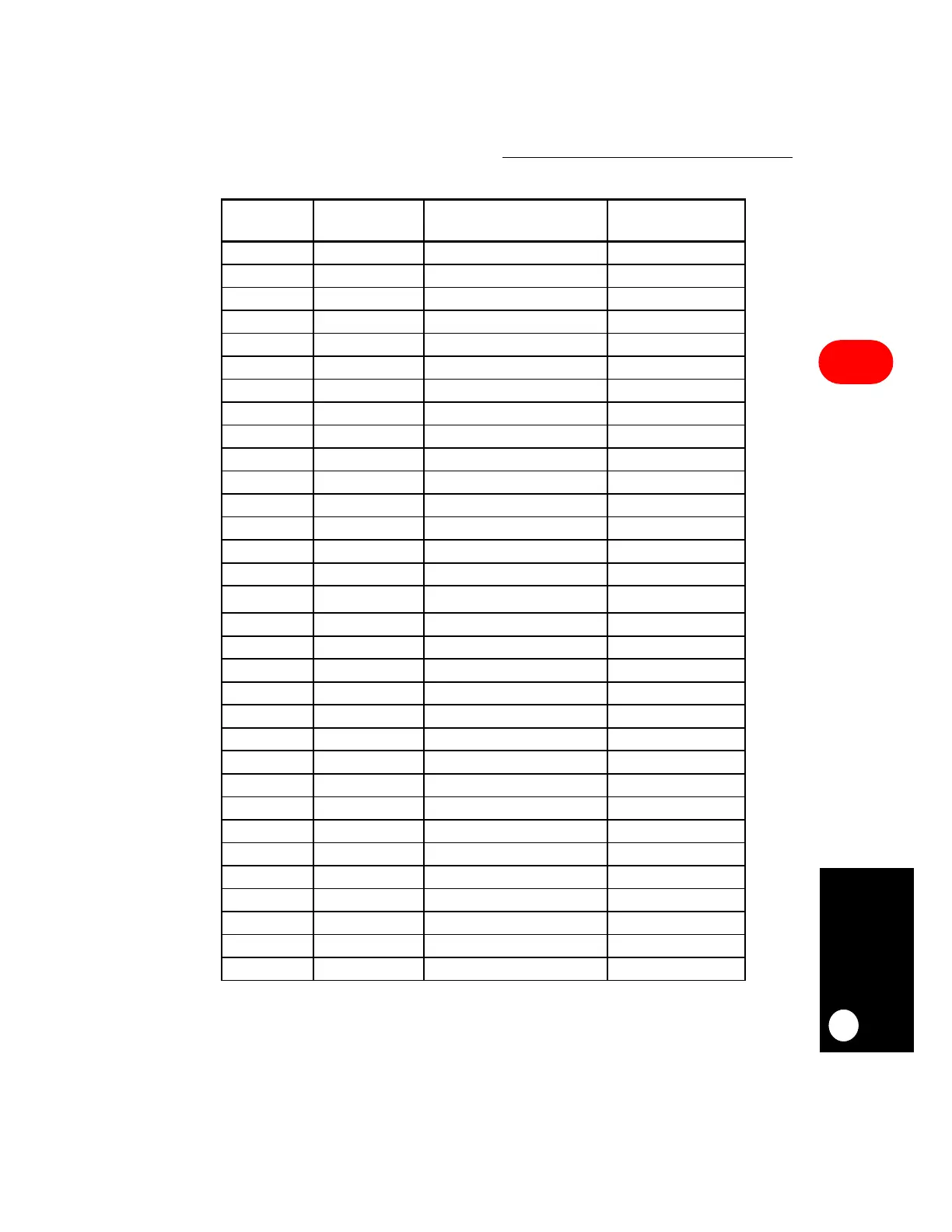

Table 16-45. Prioritization of CPM Interrupt Sources

NUMBER PRIORITY LEVEL INTERRUPT SOURCE

DESCRIPTION

MULTIPLE EVENTS

1F Highest Parallel I/O–PC15 No

1E SCCa (Grouped and Spread) Yes

1D SCCb (Grouped) Yes

1C SCCc (Grouped) Yes

1B SCCd (Grouped) Yes

1A Parallel I/O–PC14 No

19 Timer 1 Yes

18 Parallel I/O–PC13 No

17 Parallel I/O–PC12 No

16 SDMA Channel Bus Error Yes

15 IDMA1 Yes

14 IDMA2 Yes

13 SCCb (Spread) Yes

12 Timer 2 Yes

11 RISC Timer Table Yes

10

I

2

C

Yes

F Parallel I/O–PC11 No

E Parallel I/O–PC10 No

D SCCc (Spread) Yes

C Timer 3 Yes

B Parallel I/O–PC9 No

A Parallel I/O–PC8 No

9 Parallel I/O–PC7 No

8 SCCd (Spread) Yes

7 Timer 4 Yes

6 Parallel I/O–PC6 No

5 SPI Yes

4 SMC1 Yes

3 SMC2 Yes

2 Parallel I/O–PC5 No

1 Parallel I/O–PC4 No

0 Lowest Reserved —

Loading...

Loading...