S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-3

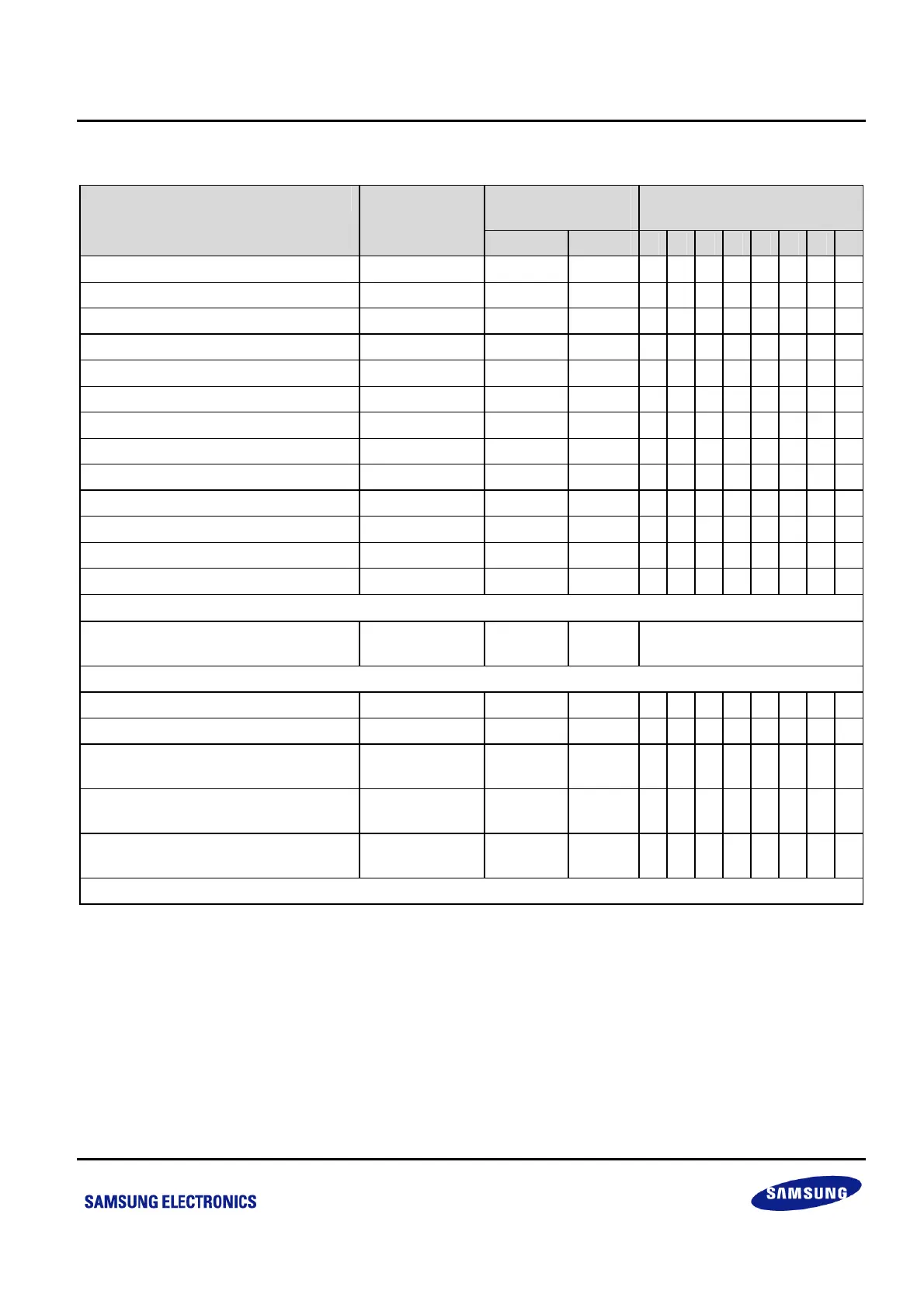

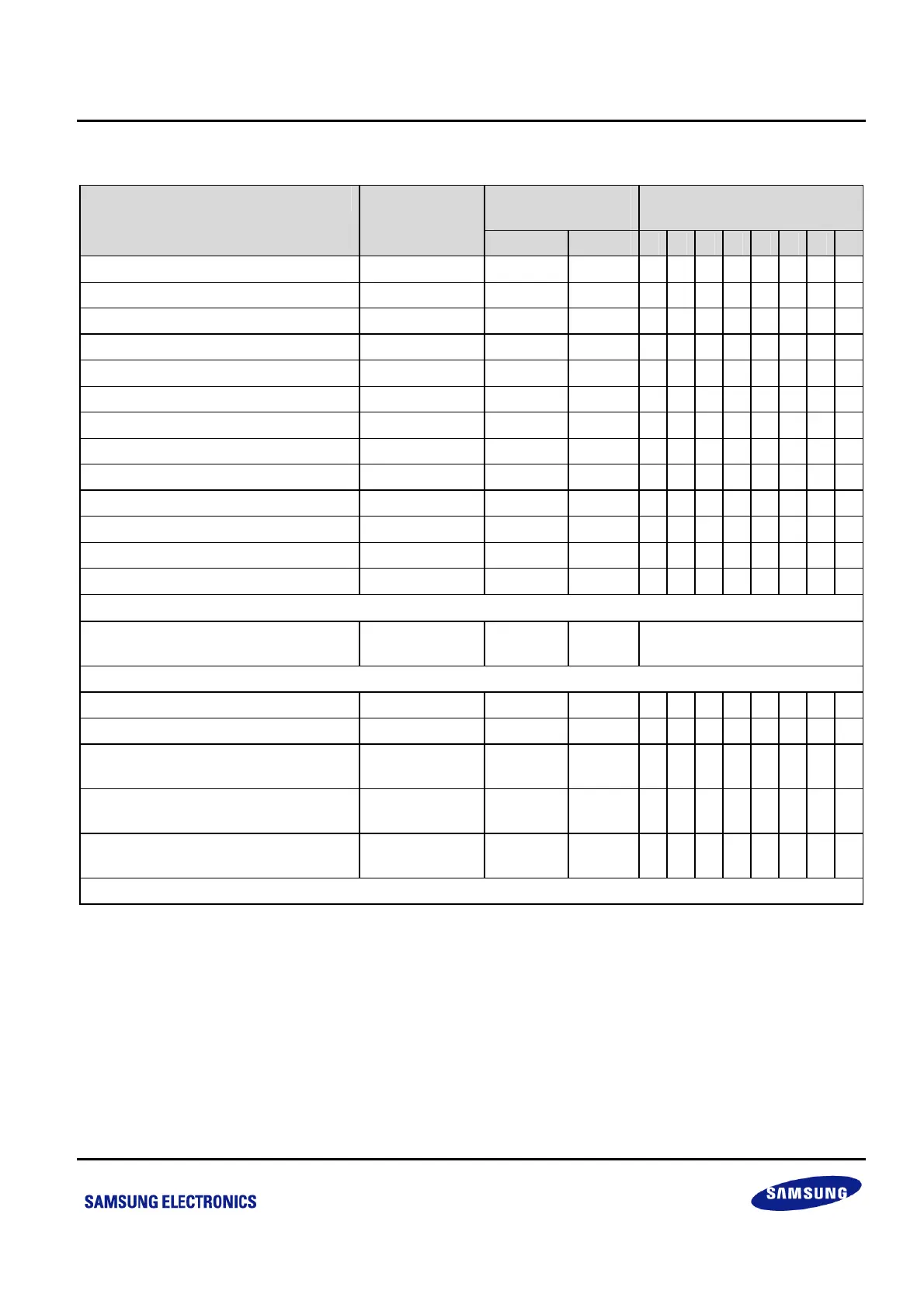

Table 4-2 System and Peripheral Control Registers Set1 Bank1

Address and

Location

RESET Value (Bit) Register Name Mnemonic

Address R/W 7 6 5 4 3 2 1 0

Operational Amplifier control register OPACON E0H R/W – – – – – – 0 0

Timer A control register TACON E1H R/W 0 0 0 0 0 0 0 0

Timer A clock pre-scalar TAPS E2H R/W 0 – – – 0 0 0 0

Timer A data register TADATA E3H R/W 1 1 1 1 1 1 1 1

Timer A counter register TACNT E4H R 0 0 0 0 0 0 0 0

Timer C control register TCCON E5H R/W 0 – 0 0 0 – 0 –

Timer C clock pre-scalar TCPS E6H R/W 0 – – – 0 0 0 0

Timer C data register TCDATA E7H R/W 1 1 1 1 1 1 1 1

Timer C counter register TCCNT E8H R x x x x x x x x

Timer D control register TDCON E9H R/W 0 0 0 0 0 0 0 0

Timer D clock pre-scalar TDPS EAH R/W 0 – – – 0 0 0 0

Timer D data register TDDATA EBH R/W 1 1 1 1 1 1 1 1

Timer D counter register TDCNT ECH R x x x x x x x x

Locations EDH-F1H are not mapped

Reset source indicating register RESETID F2H RW Refer to the detailed

description

Location F3H is not mapped

STOP control register STOPCON F4H R/W 0 0 0 0 0 0 0 0

Flash memory control register FMCON F5H R/W 0 0 0 0 0 – – 0

Flash memory user programming

enable register

FMUSR F6H R/W 0 0 0 0 0 0 0 0

Flash memory sector address register

(high byte)

FMSECH F7H R/W 0 0 0 0 0 0 0 0

Flash memory sector address register

(low byte)

FMSECL F8H R/W 0 0 0 0 0 0 0 0

Locations F9H – FFH are not mapped

NOTE: –: Not mapped or not used, x: Undefined

Loading...

Loading...