Date Code 990430 Setting the SEL-351P Recloser Control 9-37

SEL-351P Manual Técnico

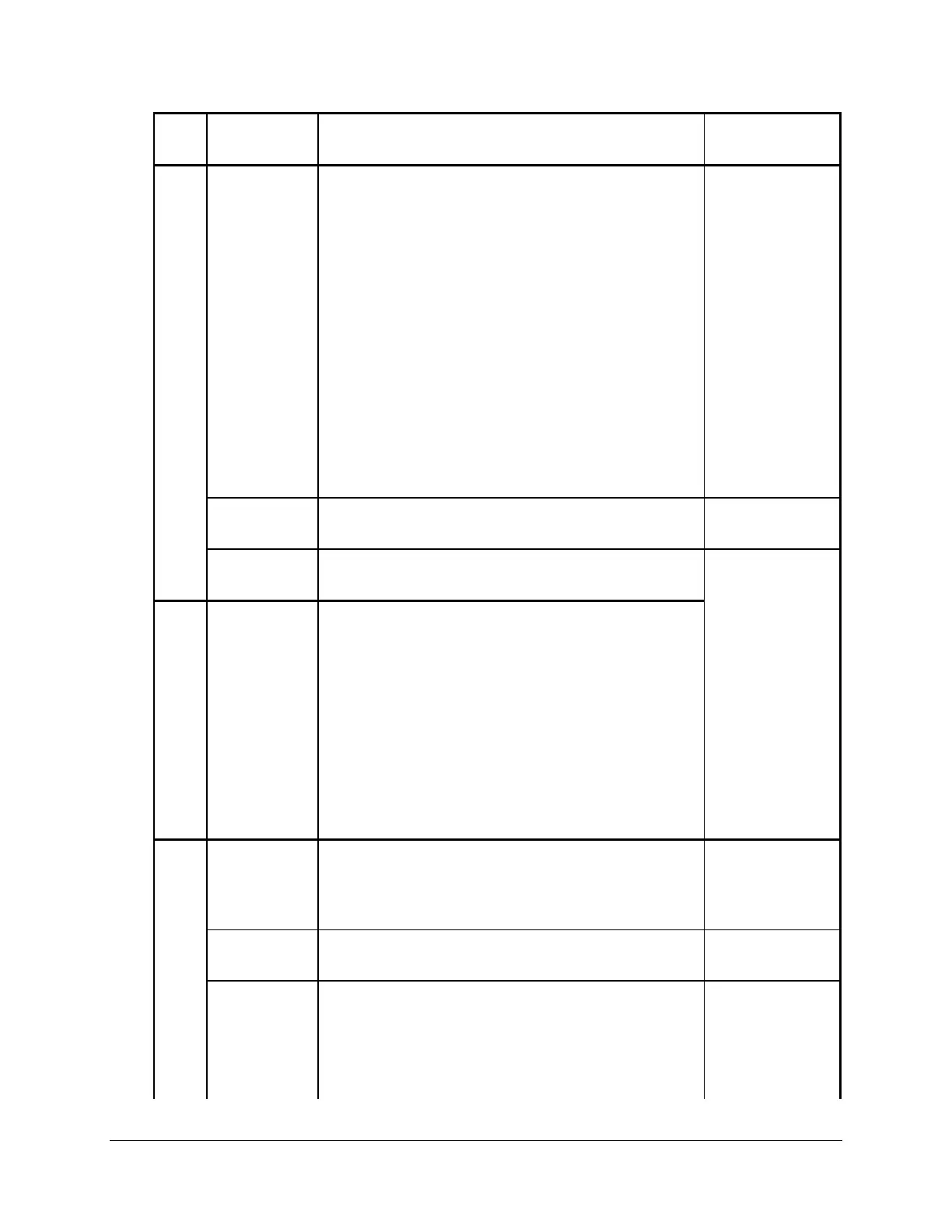

Row

Bit

Definition

Primary

Application

BCWA A-phase breaker contact wear has reached 100%

wear level (see Breaker/Recloser Contact Wear

Monitor in Section 8)

Indication

BCWB B-phase breaker contact wear has reached 100%

wear level (see Breaker/Recloser Contact Wear

Monitor in Section 8)

BCWC C-phase breaker contact wear has reached 100%

wear level (see Breaker/Recloser Contact Wear

Monitor in Section 8)

BCBOK

Battery charge board is OK (enabled) (see Battery

Sytstem Monitor in Section 8)

TOSLP Battery capacity has gone below user-set capacity

threshold and recloser control will shut down (go to

sleep) (see Battery System Monitor in Section 8)

Indication, event

or SER trigger

DISTST

Battery discharge test in progress (see Battery

System Monitor in Section 8)

Indication

DTFAIL

Battery discharge test has failed (see Battery System

Monitor in Section 8)

Alarm,

indication

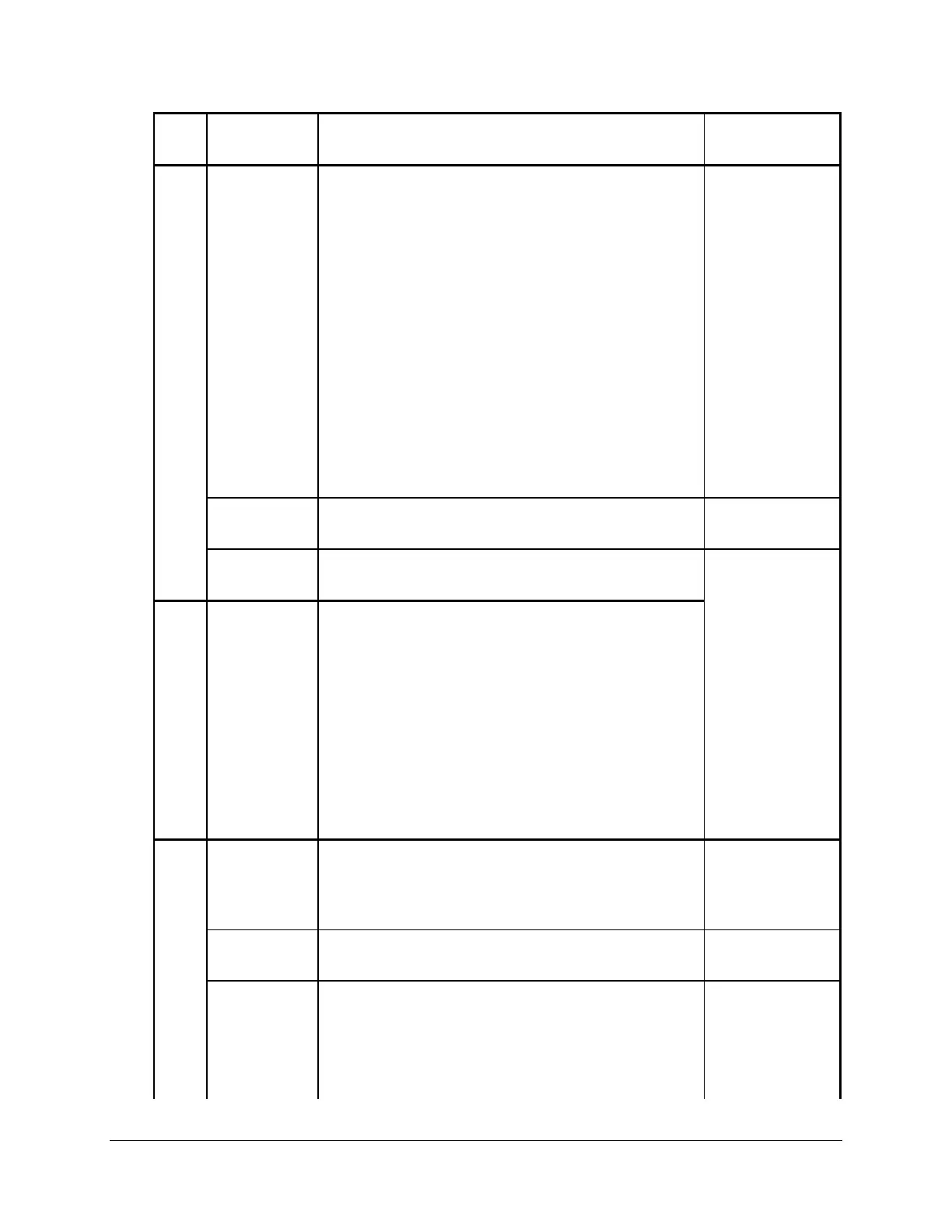

37 ALARM Output contact ALARM asserted (see Figure 7.26)

OUT107 Output contact OUT107 asserted (see Figure 7.26)

OUT106 Output contact OUT106 asserted (see Figure 7.26)

OUT105 Output contact OUT105 asserted (see Figure 7.26)

OUT104 Output contact OUT104 asserted (see Figure 7.26)

OUT103 Output contact OUT103 asserted (see Figure 7.26)

OUT102 Output contact OUT102 asserted (see Figure 7.26)

OUT101 Output contact OUT101 asserted (see Figure 7.26)

38 3PO Three pole open condition (see Figure 5.3) Testing

SOTFE Switch-onto-fault condition (see Figure 5.3)

Z3RB Zone (level) 3 reverse block (see Figure 5.6)

KEY Key permissive trip signal start (see Figure 5.6) Output contact

assignment

EKEY Echo key (see Figure 5.6) Testing

ECTT Echo conversion to trip condition (see Figure 5.6)

WFC Weak infeed condition (see Figure 5.6)

PT Permissive trip signal to POTT logic (see Figure 5.5)

Loading...

Loading...