Conventions for S7-200 Instructions

8-7

S7-200 Programmable Controller System Manual

A5E00066097-02

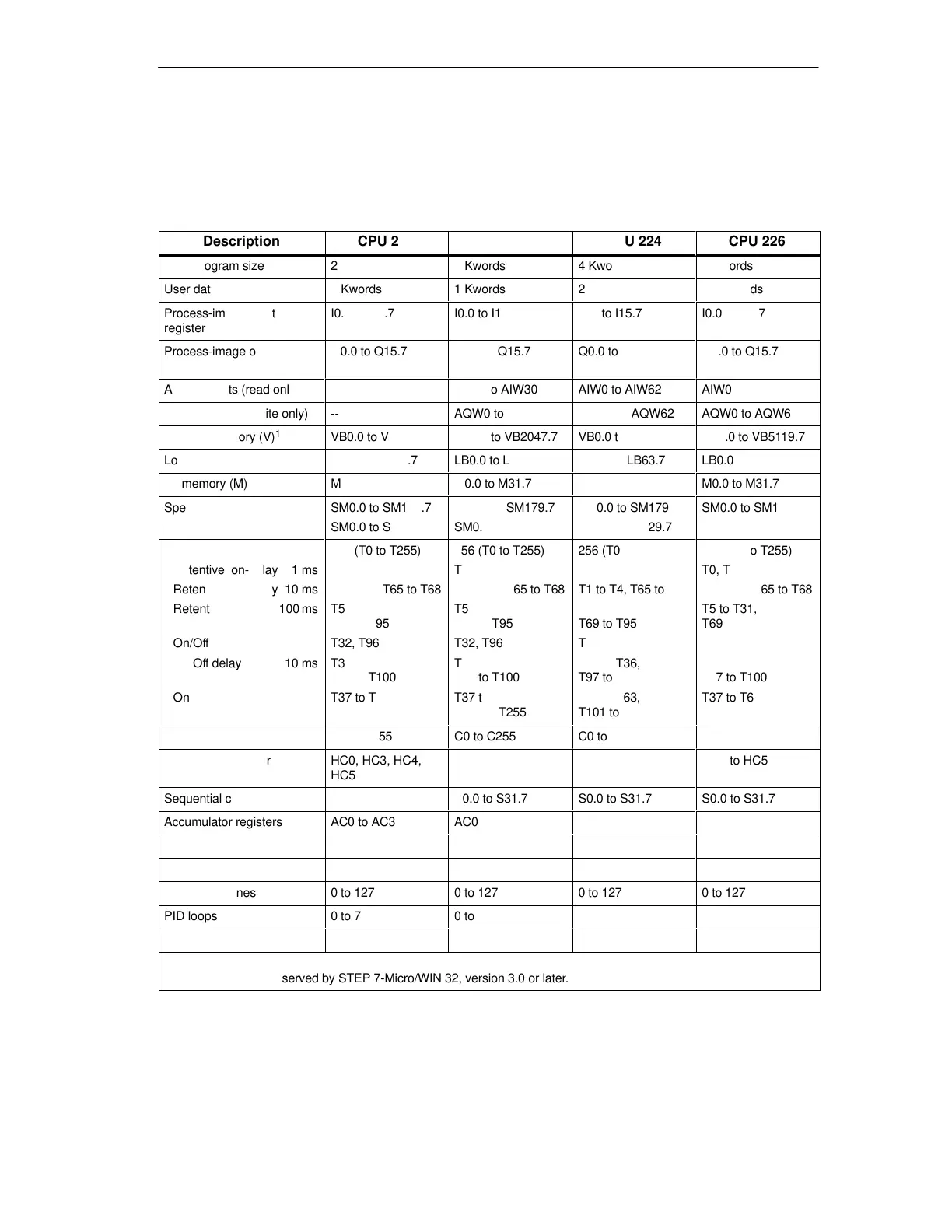

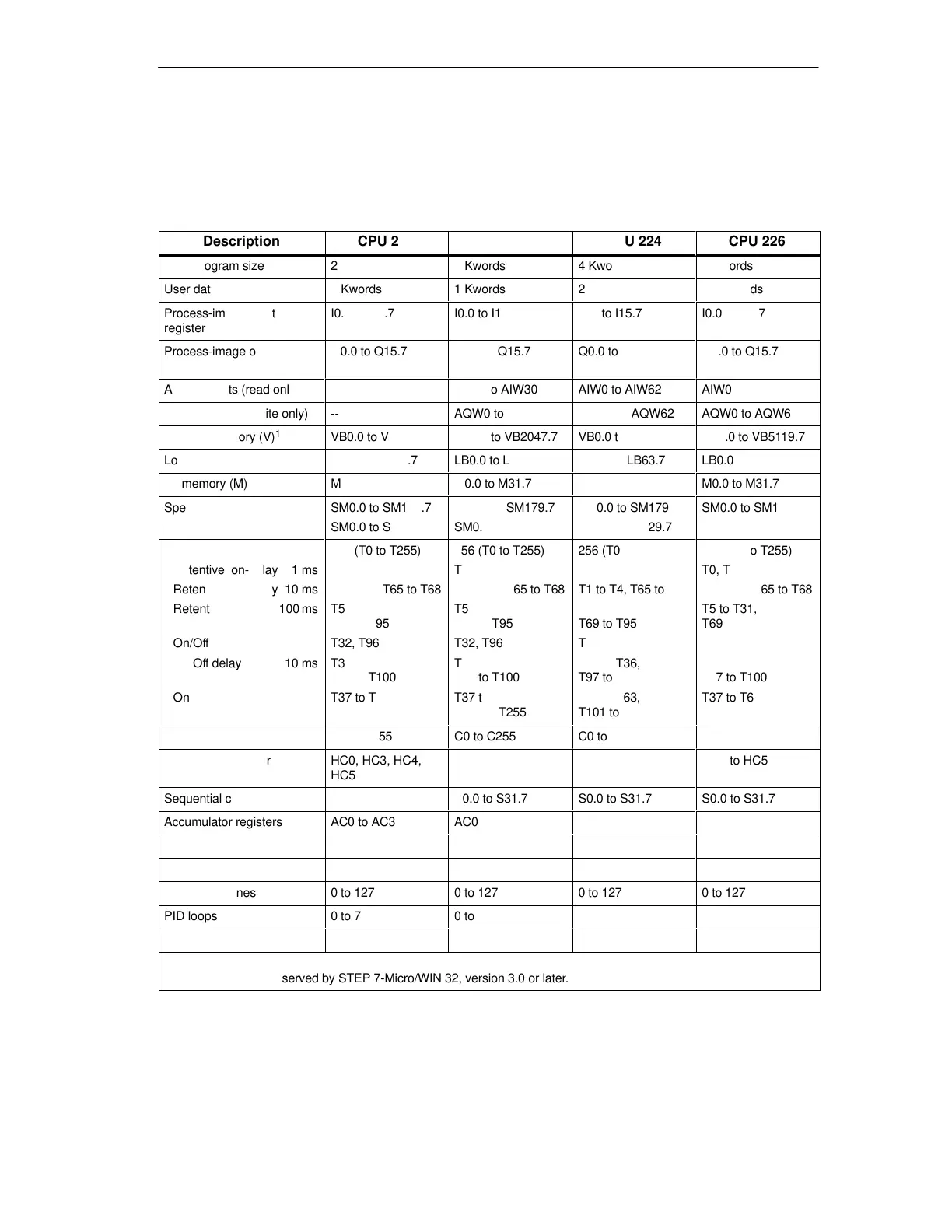

8.2 Valid Ranges for the S7-200 CPUs

Table 8-2 Summary of S7-200 CPU Memory Ranges and Features

Description

CPU 221

CPU 222

CPU 224

CPU 226

User program size

2 Kwords

2 Kwords

4 Kwords

4 Kwords

User data size

1 Kwords

1 Kwords

2.5 Kwords

2.5 Kwords

ÁÁÁÁÁÁ

Process-image input

register

ÁÁÁÁ

I0.0 to I15.7

ÁÁÁÁ

I0.0 to I15.7

ÁÁÁÁ

I0.0 to I15.7

ÁÁÁÁ

I0.0 to I15.7

Process-image output

register

Q0.0 to Q15.7

Q0.0 to Q15.7

Q0.0 to Q15.7

Q0.0 to Q15.7

Analog inputs (read only)

--

AIW0 to AIW30

AIW0 to AIW62

AIW0 to AIW62

Analog outputs (write only)

--

AQW0 to AQW30

AQW0 to AQW62

AQW0 to AQW62

Variable memory (V)

1

VB0.0 to VB2047.7

VB0.0 to VB2047.7

VB0.0 to VB5119.7

VB0.0 to VB5119.7

Local memory (L)

2

LB0.0 to LB63.7

LB0.0 to LB63.7

LB0.0 to LB63.7

LB0.0 to LB63.7

Bit memory (M)

M0.0 to M31.7

M0.0 to M31.7

M0.0 to M31.7

M0.0 to M31.7

ÁÁÁÁÁÁ

Special Memory (SM)

Read only

ÁÁÁÁ

SM0.0 to SM179.7

SM0.0 to SM29.7

ÁÁÁÁ

SM0.0 to SM179.7

SM0.0 to SM29.7

ÁÁÁÁ

SM0.0 to SM179.7

SM0.0 to SM29.7

ÁÁÁÁ

SM0.0 to SM179.7

SM0.0 to SM29.7

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

ÁÁÁÁÁÁ

Timers

Retentive on-delay 1 ms

Retentive on-delay 10 ms

Retentive on-delay 100 ms

On/Off delay 1 ms

On/Off delay 10 ms

On/Off delay 100 ms

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

256 (T0 to T255)

T0, T64

T1 to T4, T65 to T68

T5 to T31,

T69 to T95

T32, T96

T33 to T36,

T97 to T100

T37 to T63,

T101 to T255

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

256 (T0 to T255)

T0, T64

T1 to T4, T65 to T68

T5 to T31,

T69 to T95

T32, T96

T33 to T36,

T97 to T100

T37 to T63,

T101 to T255

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

256 (T0 to T255)

T0, T64

T1 to T4, T65 to T68

T5 to T31,

T69 to T95

T32, T96

T33 to T36,

T97 to T100

T37 to T63,

T101 to T255

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

ÁÁÁÁ

256 (T0 to T255)

T0, T64

T1 to T4, T65 to T68

T5 to T31,

T69 to T95

T32, T96

T33 to T36,

T97 to T100

T37 to T63,

T101 to T255

Counters

C0 to C255

C0 to C255

C0 to C255

C0 to C255

ÁÁÁÁÁÁ

High-speed counter

ÁÁÁÁ

HC0, HC3, HC4,

HC5

ÁÁÁÁ

HC0, HC3, HC4,

HC5

ÁÁÁÁ

HC0 to HC5

ÁÁÁÁ

HC0 to HC5

Sequential control relays (S)

S0.0 to S31.7

S0.0 to S31.7

S0.0 to S31.7

S0.0 to S31.7

Accumulator registers

AC0 to AC3

AC0 to AC3

AC0 to AC3

AC0 to AC3

Jumps/Labels

0 to 255

0 to 255

0 to 255

0 to 255

Call/Subroutine

0 to 63

0 to 63

0 to 63

0 to 63

Interrupt routines

0 to 127

0 to 127

0 to 127

0 to 127

PID loops

0 to 7

0 to 7

0 to 7

0 to 7

Port

Port 0

Port 0

Port 0

Port 0, Port 1

ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ

ÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁÁ

1

All V memory can be saved to permanent memory.

2

LB60 to LB63 are reserved by STEP 7-Micro/WIN 32, version 3.0 or later.

Loading...

Loading...