SIMATIC Instructions

9-39

S7-200 Programmable Controller System Manual

A5E00066097-02

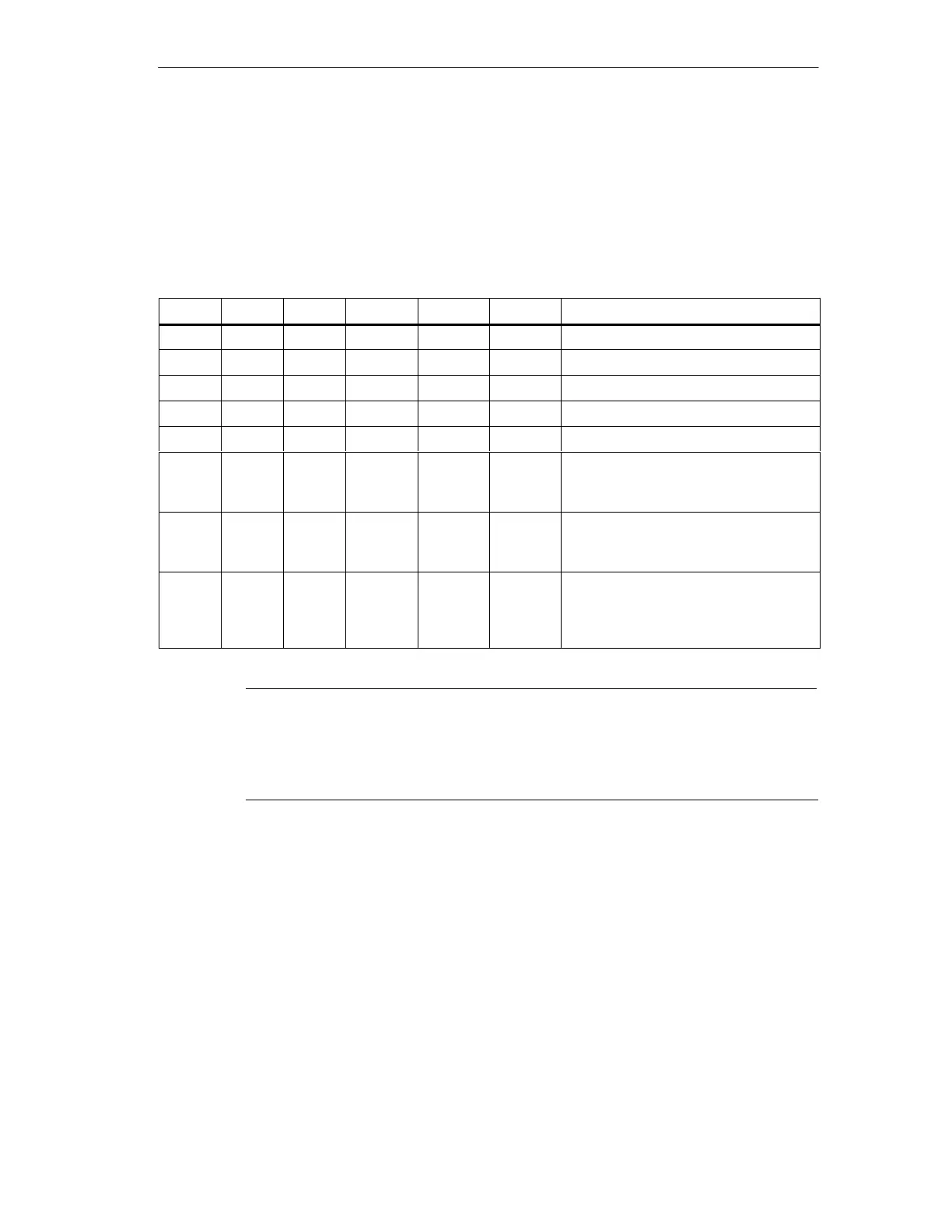

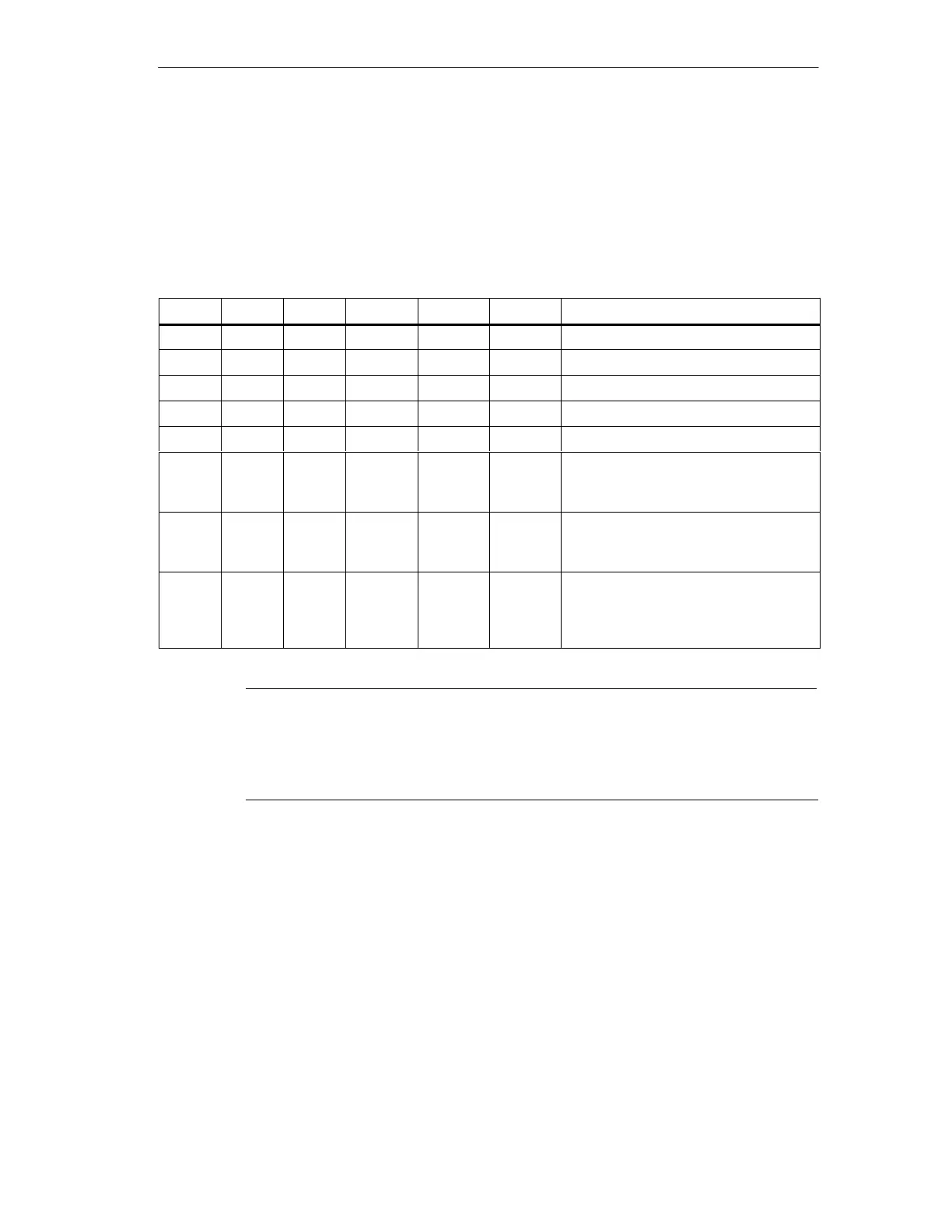

Status Byte

A status byte is provided for each high-speed counter that provides status memory

bits that indicate the current counting direction, and whether the current value is

greater or equal to the preset value. Table 9-14 defines these status bits for each

high-speed counter.

Table 9-14 Status Bits for HSC0, HSC1, HSC2, HSC3, HSC4, and HSC5

HSC0

HSC1 HSC2 HSC3 HSC4 HSC5 Description

SM36.0 SM46.0 SM56.0 SM136.0 SM146.0 SM156.0 Not used

SM36.1 SM46.1 SM56.1 SM136.1 SM146.1 SM156.1 Not used

SM36.2 SM46.2 SM56.2 SM136.2 SM146.2 SM156.2 Not used

SM36.3 SM46.3 SM56.3 SM136.3 SM146.3 SM156.3 Not used

SM36.4 SM46.4 SM56.4 SM136.4 SM146.4 SM156.4 Not used

SM36.5 SM46.5 SM56.5 SM136.5 SM146.5 SM156.5 Current counting direction status bit:

0 = counting down;

1 = counting up

SM36.6 SM46.6 SM56.6 SM136.6 SM146.6 SM156.6 Current value equals preset value

status bit:

0 = not equal; 1 = equal

SM36.7 SM46.7 SM56.7 SM136.7 SM146.7 SM156.7 Current value greater than preset value

status bit:

0 = less than or equal;

1 = greater than

Note

Status bits are valid only while the high-speed counter interrupt routine is being

executed. The purpose of monitoring the state of the high-speed counter is to

enable interrupts for the events that are of consequence to the operation being

performed.

HSC Interrupts

All counter modes support an interrupt on current value equal to the preset value.

Counter modes that use an external reset input support an interrupt on external

reset activated. All counter modes except modes 0, 1, and 2 support an interrupt

on a counting direction change. Each of these interrupt conditions may be enabled

or disabled separately. For a complete discussion on the use of interrupts, see

Section 9.15

.

Loading...

Loading...