SFR ACC,T

6-326

SFR ACC,T Shift Accumulator Right

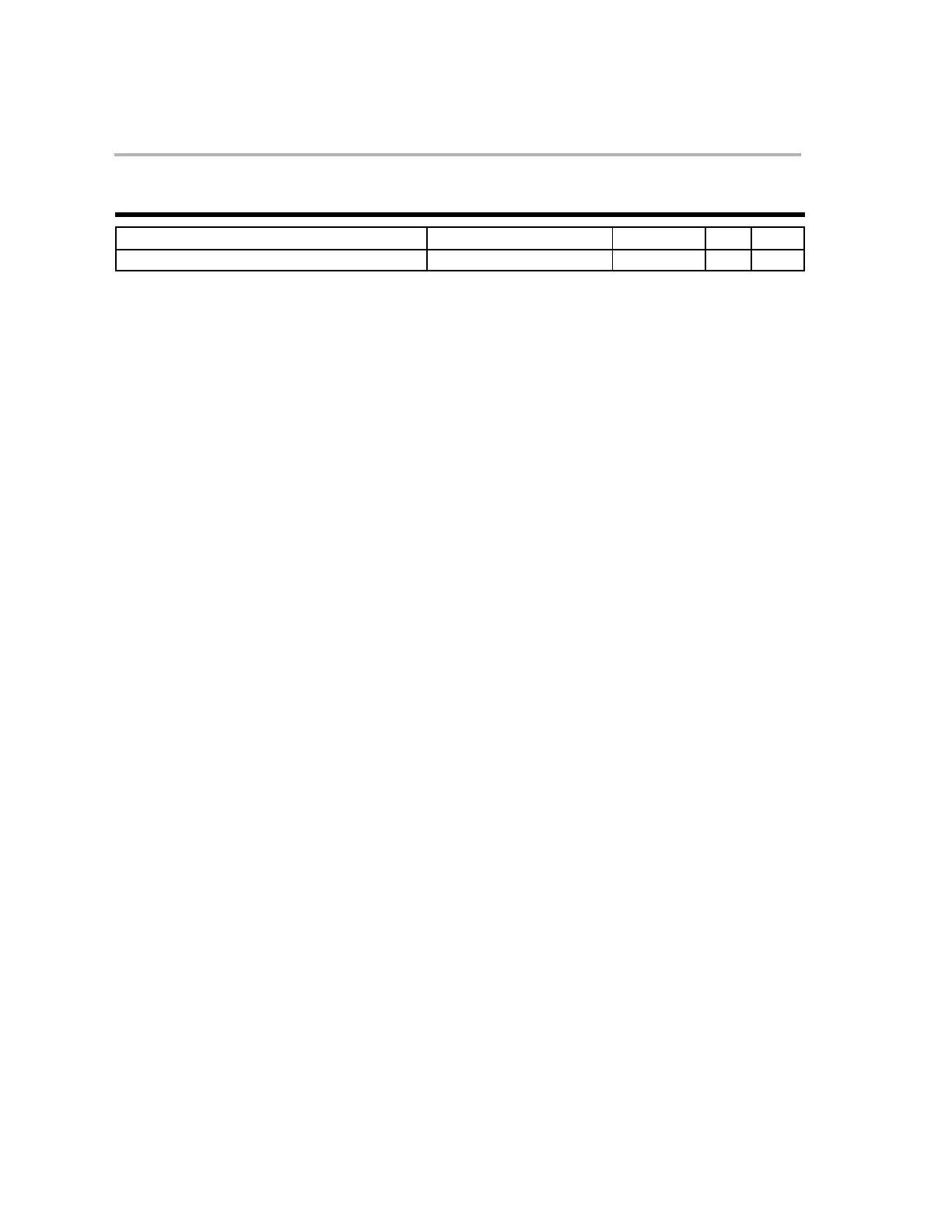

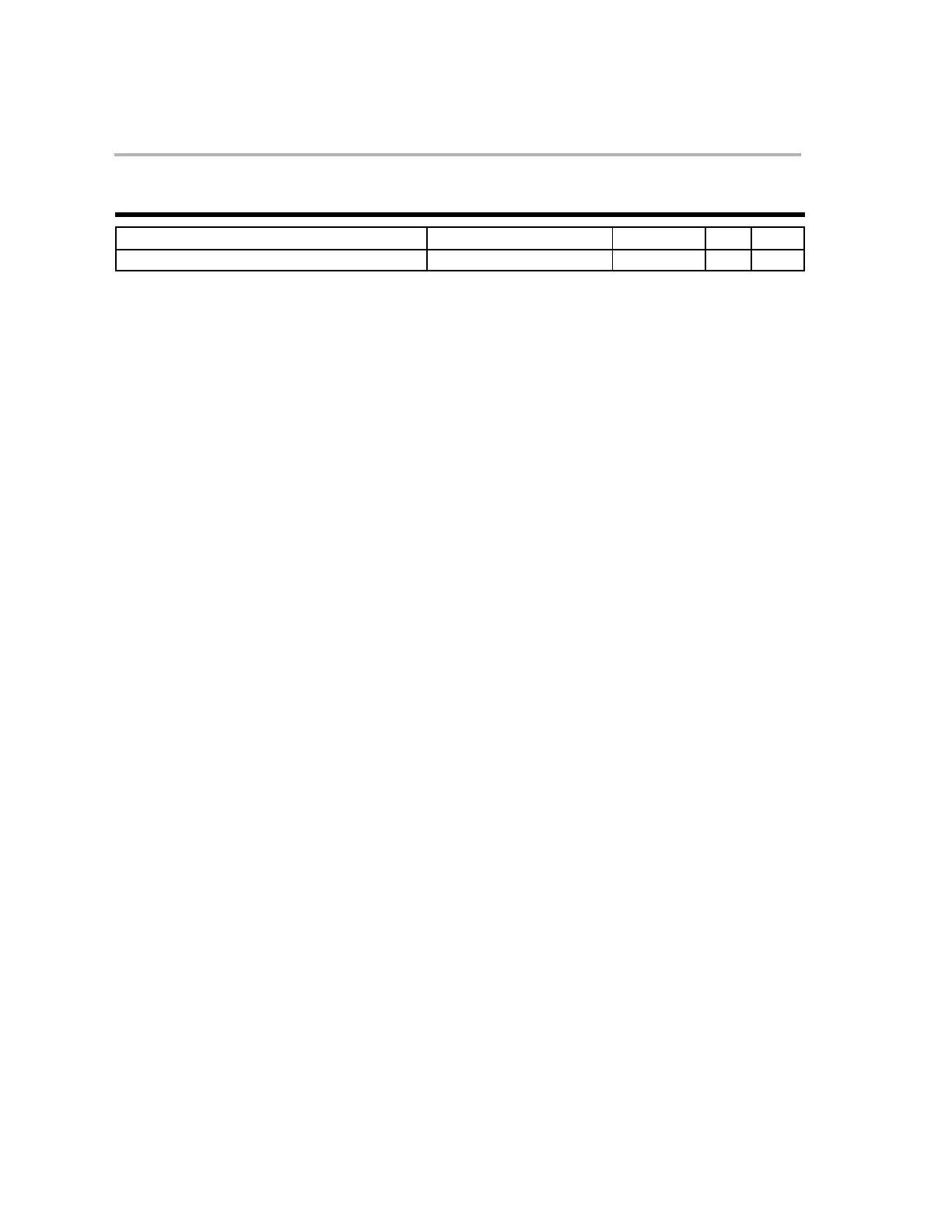

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

SFR ACC,T 1111 1111 0101 0001 X − 1

Operands ACC Accumulator register

T Upper 16-bits of the multiplicand (XT) register

Description Right shift the content of the ACC register by the amount specified in the four

least significant bits of the T register, T(3:0) = 0..15. Higher order bits are

ignored. The type of shift (arithmetic or logical) is determined by the state of

the sign extension mode (SXM) bit:

if(SXM = 1) // sign extension mode enabled

ACC = S:ACC >> T(3:0); // arithmetic shift right

else // sign extension mode disabled

ACC = 0:ACC >> T(3:0); // logical shift right

Flags and

Modes

Z After the shift, the Z flag is set if the ACC value is zero, else Z is cleared. Even

if the T register specifies a shift of 0, the content of the ACC register is still

tested for the zero condition and Z is affected.

N After the shift, the N flag is set if bit 31 of the ACC is 1, else N is cleared. Even

if the T register specifies a shift of 0, the content of the ACC register is still

tested for the negative condition and N is affected.

C If (T(3:0) = 0) then C is cleared; otherwise, the last bit shifted out is loaded

into the C flag bit.

SXM if (SXM = 1), then the operation behaves like an arithmetic right shift.

If (SXM = 0), then the operation behaves like a logical right shift.

Repeat This instruction is repeatable. If the operation follows a RPT instruction, then

the SFR instruction will be executed N+1 times. The state of the Z, N and C

flags will reflect the final result.

Example

; Arithmetic shift right contents of VarA by VarB:

MOVL ACC,@VarA ; ACC = VarA

MOV T,@VarB ; T = VarB (shift value)

SETC SXM ; Enable sign extension mode

SFR ACC,T ; Arithmetic shift right ACC by T(3:0)

MOVL @VarA,ACC ; Store result into VarA

Loading...

Loading...