SUBUL P,loc32

6-358

SUBUL P,loc32 Subtract Unsigned 32-bit Value

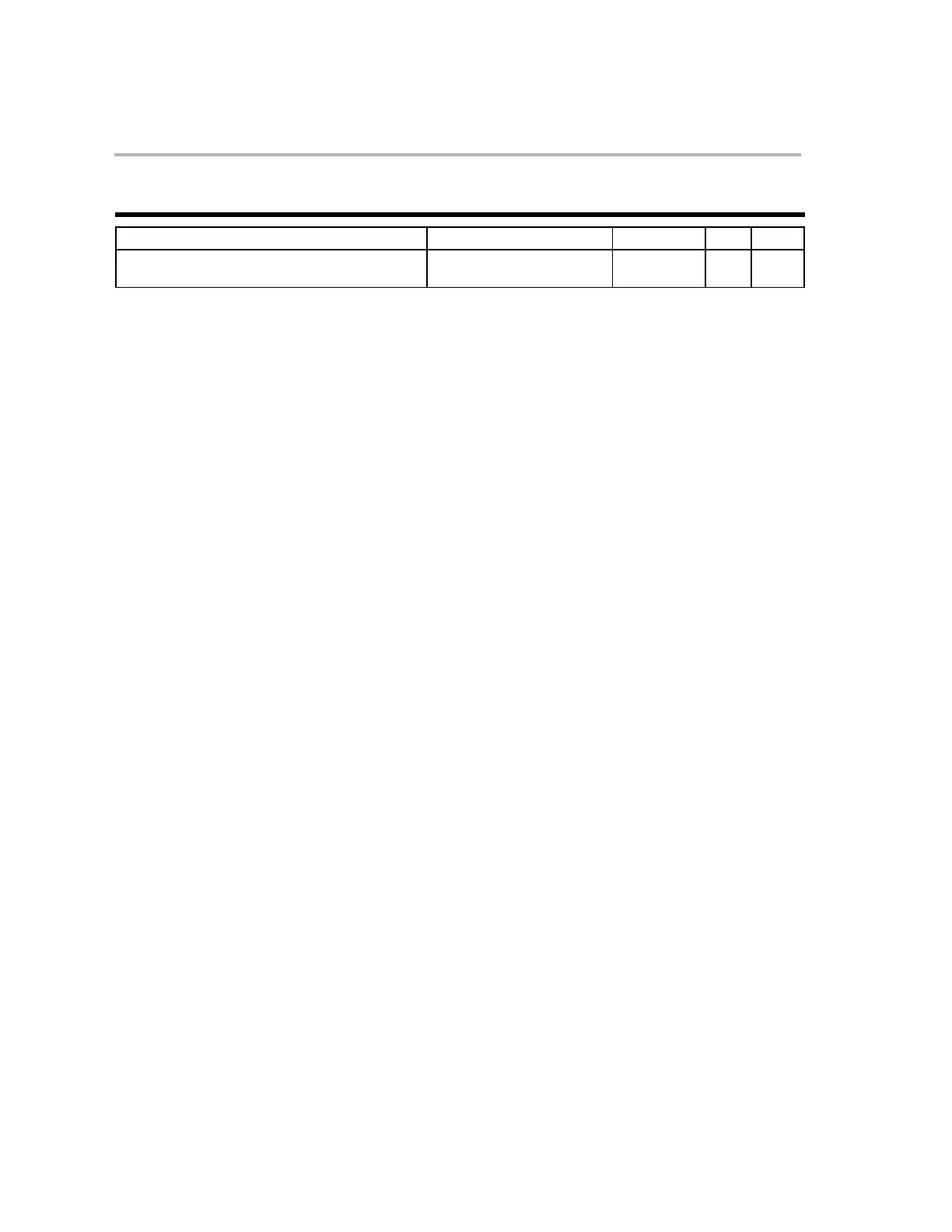

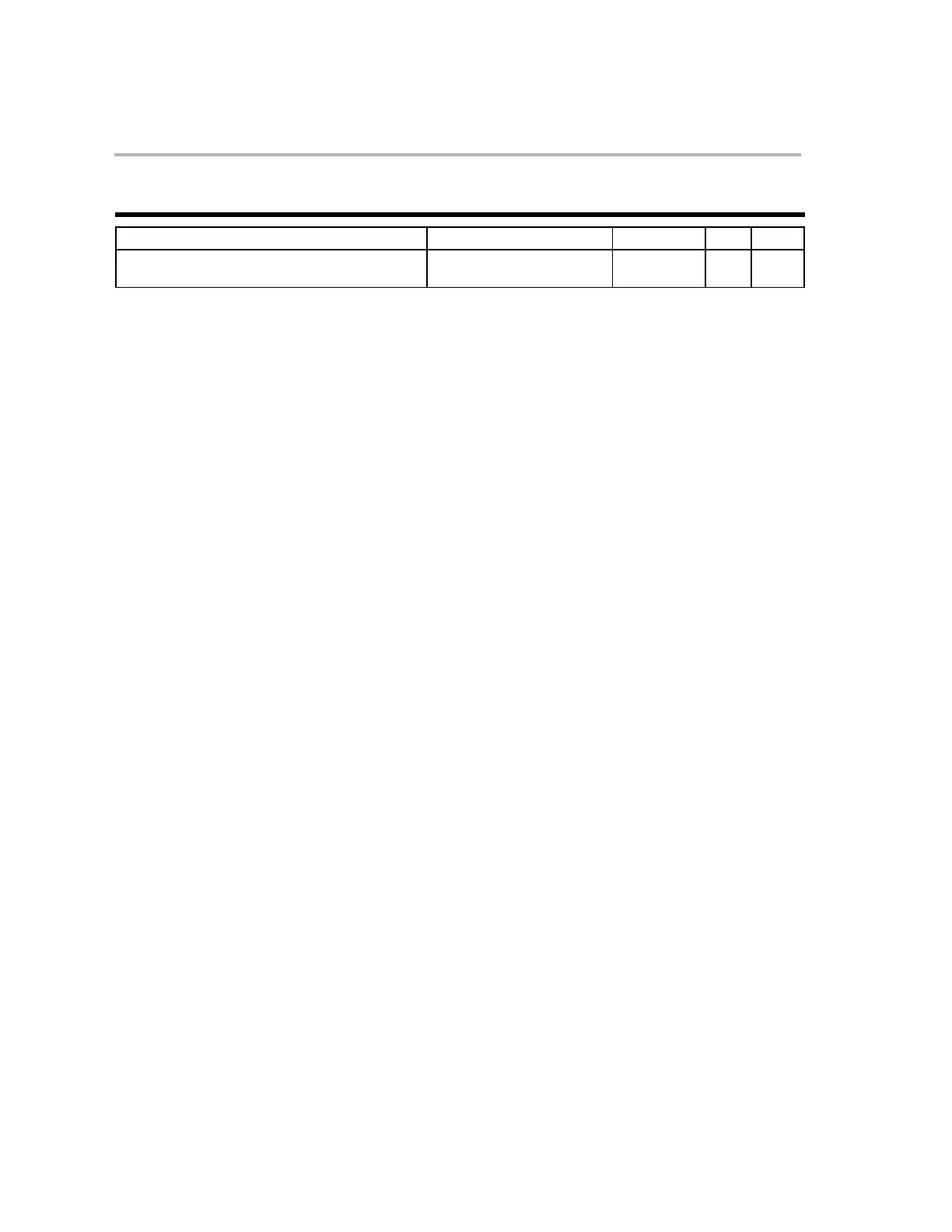

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

SUBUL P,loc32

0101 0110 0101 1101

0000 0000 LLLL LLLL

1 − 1

Operands P Product register

loc32 Addressing mode (see Chapter 5)

Description Subtract from the P register the 32-bit content of the location pointed to by

the “loc32” addressing mode. The addition is treated as an unsigned SUB

operation:

P = P − [loc32]; // unsigned subtract

Note: The difference between a signed and unsigned 32-bit subtract is in the treatment of the

overflow counter (OVC). For a signed SUBL, the OVC counter monitors

positive/negative overflow. For an unsigned SUBL, the OVC unsigned (OVCU) counter

monitors the borrow.

Flags and

Modes

Z After the subtraction, the Z flag is set if the P value is zero, else Z is cleared.

N After the subtraction, the N flag is set if bit 31 of P is 1, else N is cleared.

C If the subtraction generates a borrow, C is cleared; otherwise C is set.

V If a signed overflow occurs, V is set; otherwise V is not affected.

OVCU The overflow counter is decremented whenever a subtraction operation

generates an unsigned borrow. The OVM mode does not affect the OVCU

counter.

Repeat This instruction is not repeatable. If this instruction follows the RPT

instruction, it resets the repeat counter (RPTC) and executes only once.

Example

; Subtract 64-bit VarA − VarB and store result in VarC:

MOVL P,@VarA+0 ; Load P with low 32-bits of VarA

MOVL ACC,@VarA+2 ; Load ACC with high 32-bits of VarA

SUBUL P,@VarB+0 ; Sub from P unsigned low 32-bits of VarB

SUBBL ACC,@VarB+2 ; Sub from ACC with borrow high 32-bits of VarB

MOVL @VarC+0,P ; Store low 32-bit result into VarC

MOVL @VarC+2,ACC ; Store high 32-bit result into VarC

Loading...

Loading...