TRAP #VectorNumber

6-363

TRAP #VectorNumber Software Trap

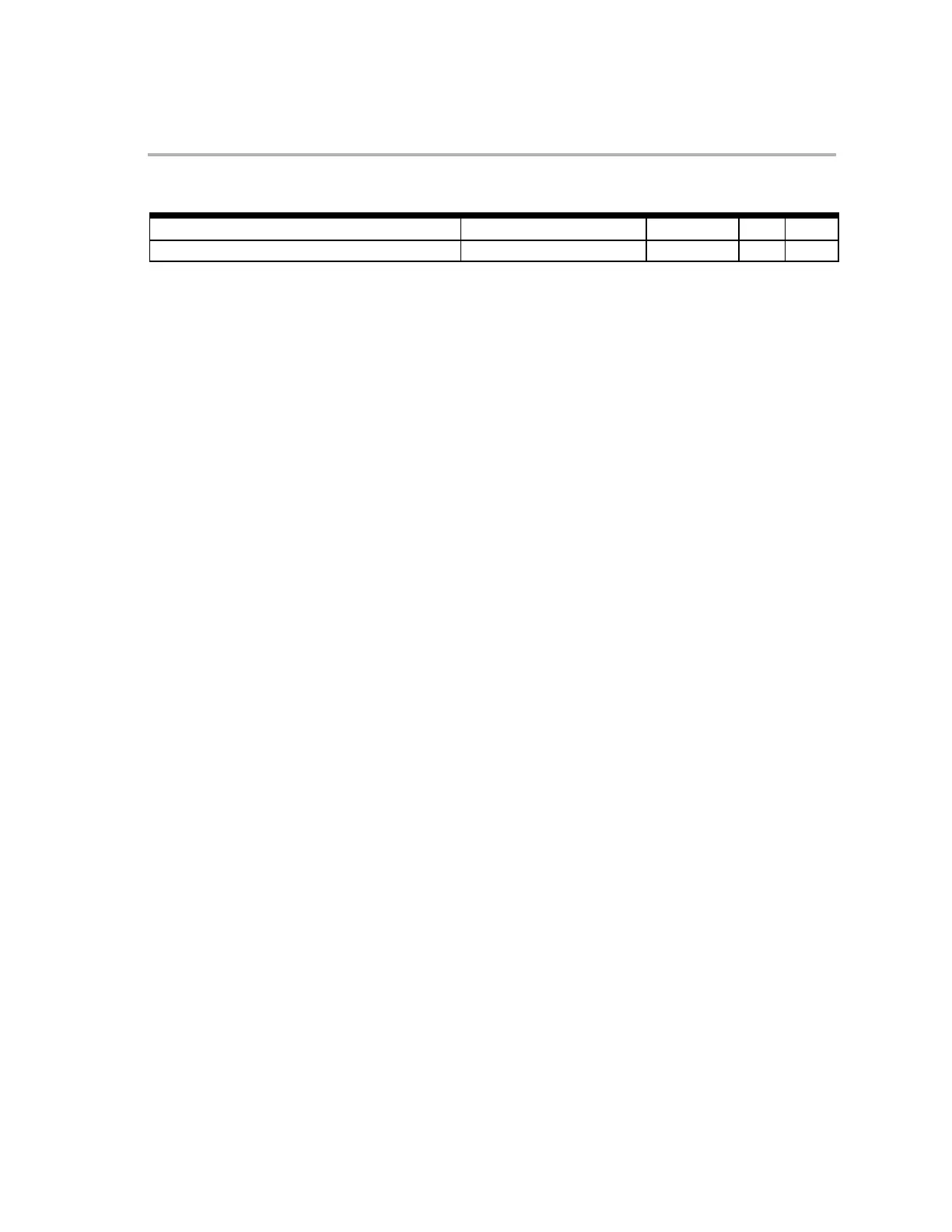

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

TRAP #VectorNumber 0000 0000 001C CCCC X − 8

Operands Vector

Number

CPU interrupt vector 0 to 31

Description The TRAP instruction transfers program control to the interrupt service

routine that corresponds to the vector specified in the instruction. It does

not affect the interrupt flag register (IFR) or the interrupt enable register

(IER), regardless of whether the chosen interrupt has corresponding bits in

these registers. The TRAP instruction is not affected by the interrupt global

mask bit (INTM) in status register ST1. It also not affected by the enable bits

in the IER or the debug interrupt enable register (DBGIER). Once the TRAP

instruction reaches the decode phase of the pipeline, hardware interrupts

cannot be serviced until the TRAP instruction is done executing (until the

interrupt service routine begins).

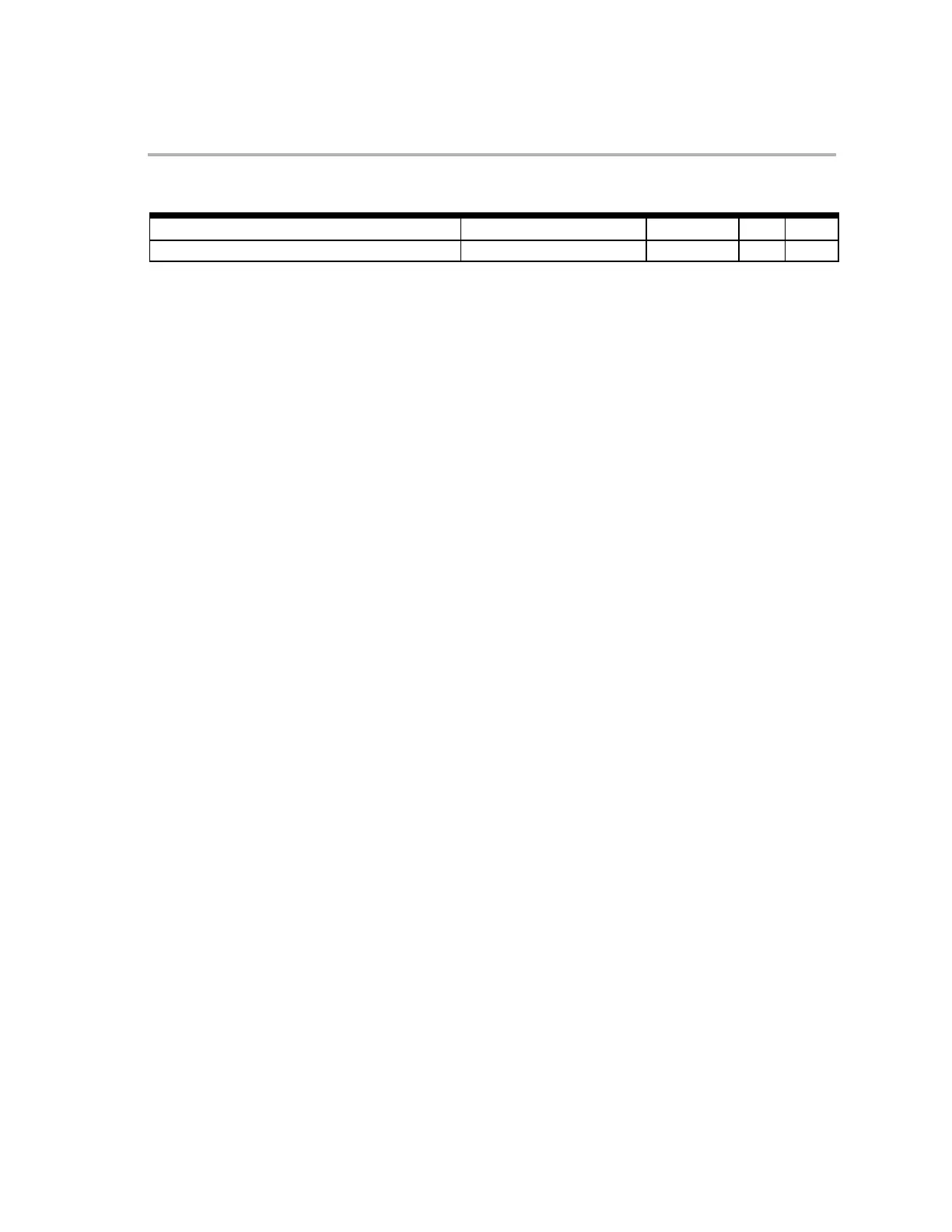

The following table indicates which interrupt vector is associated with a

chosen value for the VectorNumber operand:

Vector

Number

Interrupt

Vector

Vector

Number

Interrupt

Vector

0 RESET 16 RTOSINT

1 INT1 17 Reserved

2 INT2 18 NMI

3 INT3 19 ILLEGAL

4 INT4 20 USER1

5 INT5 21 USER2

6 INT6 22 USER3

7 INT7 23 USER4

8 INT8 24 USER5

9 INT9 25 USER6

10 INT10 26 USER7

11 INT11 27 USER8

12 INT12 28 USER9

13 INT13 29 USER10

14 INT14 30 USER11

15 DLOGINT 31 USER12

Loading...

Loading...