00 = sync to SYSCLKOUT only *

01 = qual to 3 samples

10 = qual to 6 samples

11 = no sync or qual (for peripheral only; GPIO same as 00)

00h no qualification (SYNC to SYSCLKOUT) *

01h QUALPRD = SYSCLKOUT/2

02h QUALPRD = SYSCLKOUT/4

… … …

FFh QUALPRD = SYSCLKOUT/510

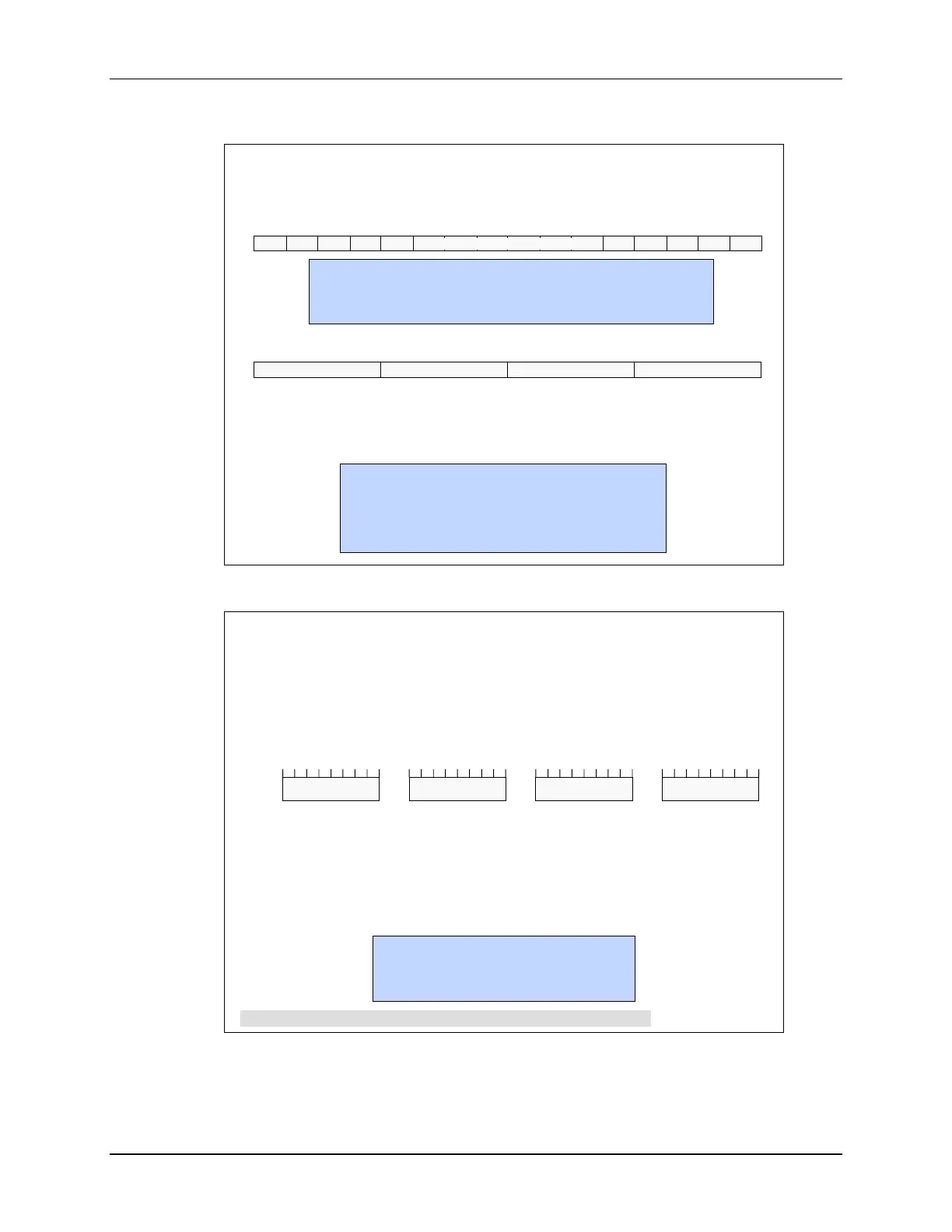

F28x7x GPIO Input Qual Registers

GpioCtrlRegs.register (lab file: Gpio.c)

GPxQSEL1 / GPxQSEL2 where x = A, B, C, D, E or F

16 pins configured per register

0

31

QUALPRD0QUALPRD1QUALPRD2QUALPRD3

GPxCTRL where x = A, B, C, D, E or F

31 24 16 8 0

A: GPIO31-24 GPIO23-16 GPIO15-8 GPIO7-0

B: GPIO63-56 GPIO55-48 GPIO47-40 GPIO39-32

C: GPIO95-88 GPIO87-80 GPIO79-72 GPIO71-64

D: GPIO127-120 GPIO119-112 GPIO111-104 GPIO103-96

E: GPIO159-152 GPIO151-144 GPIO143-136 GPIO135-128

F: GPIO191-184 GPIO183-176 GPIO175-168 GPIO167-160

* reset default

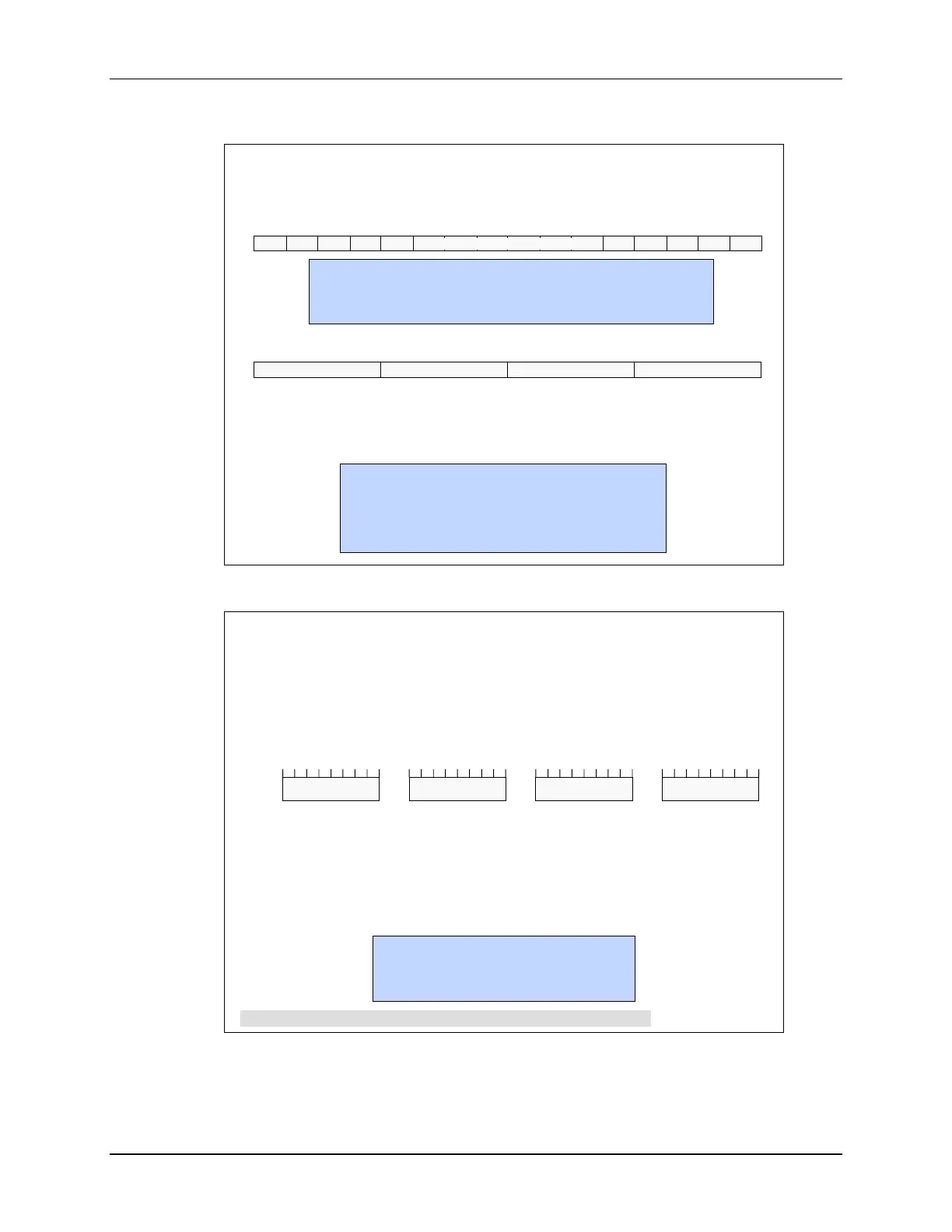

F28x7xD Dual-Core GPIO Core Select

GpioCtrlRegs.register (lab file: Gpio.c)

Selects which core’s GPIODAT/SET/CLEAR/TOGGLE

registers are used to control a pin

Each pin individually controlled

xx00 pin controlled by CPU1 *

xx01 pin controlled by CPU1.CLA1

xx10 pin controlled by CPU2

xx11 pin controlled by CPU2.CLA1

A: GPIO31-24 GPIO23-16 GPIO15-8 GPIO7-0

B: GPIO63-56 GPIO55-48 GPIO47-40 GPIO39-32

C: GPIO95-88 GPIO87-80 GPIO79-72 GPIO71-64

D: GPIO127-120 GPIO119-112 GPIO111-104 GPIO103-96

E: GPIO159-152 GPIO151-144 GPIO143-136 GPIO135-128

F: GPIO191-184 GPIO183-176 GPIO175-168 GPIO167-160

* reset default

GPxCSEL1

031

GPxCSEL3

031

GPxCSEL4

031

GPxCSEL2

031

Note: GPxLOCK register can be used to lock above registers (lock bit for each pin)

Loading...

Loading...