0

0.0

0.1

0.2

0.3

1

1.0

1.1

1.2

1.3

31

31.0

31.1

31.2

31.3

TRIPINx

TRIPOUTPUTINV

TRIPxMUXENABLE

TRIPxMUX0TO15CFG.MUX0

TRIPxMUX0TO15CFG.MUX1

TRIPxMUX16TO31CFG.MUX31

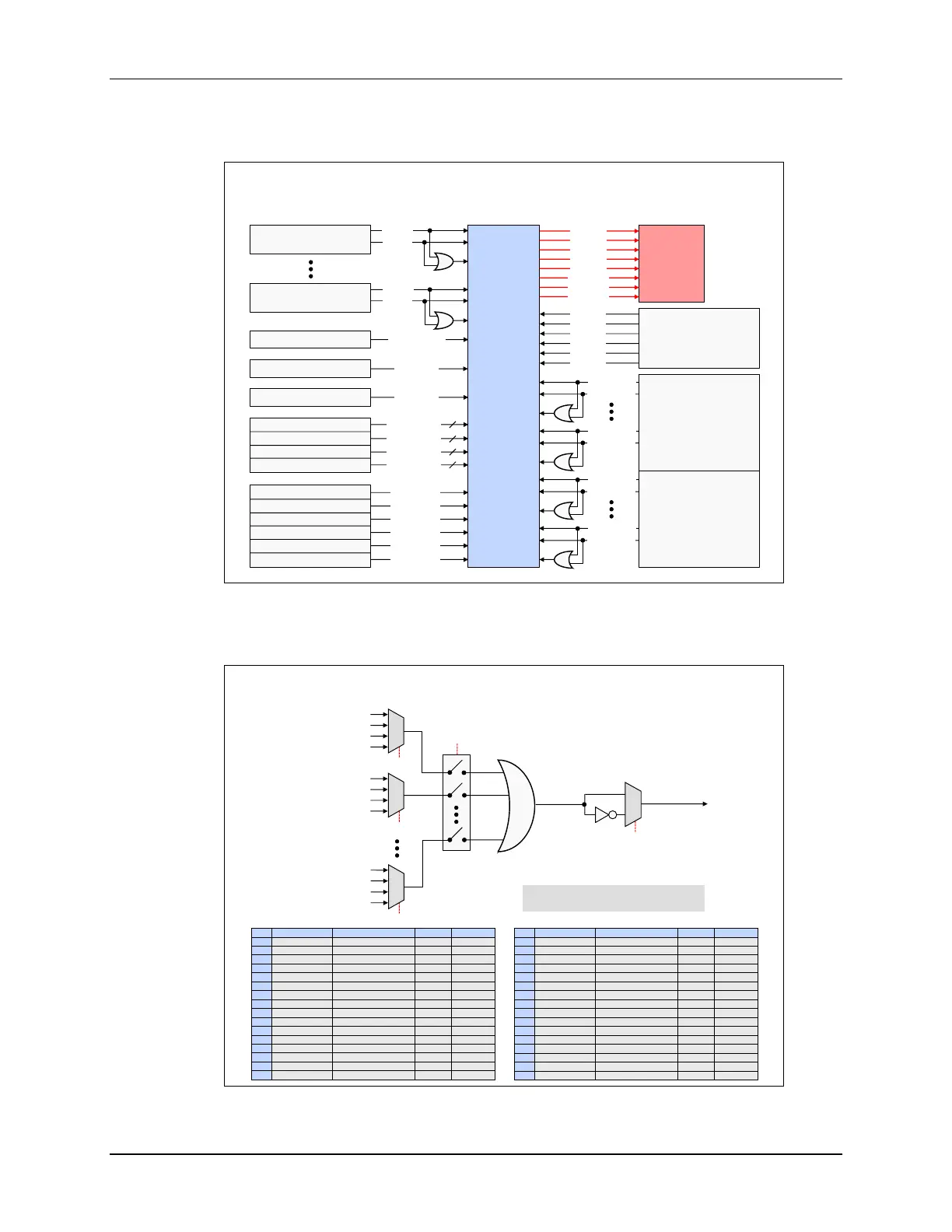

ePWM X-Bar Architecture

MUX 0 1 2 3

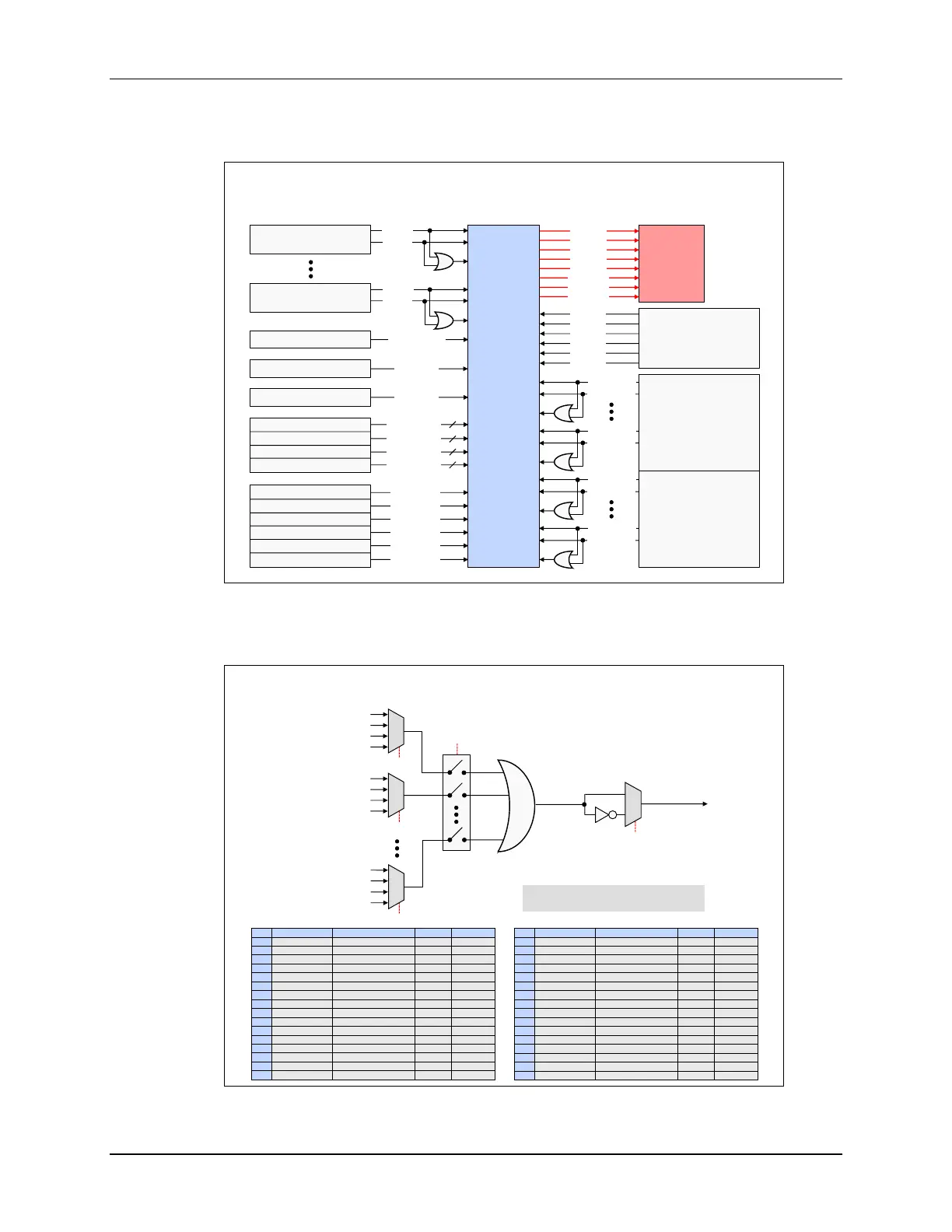

16 SD1FLT1.COMPH SD1FLT1.COMPH_OR_COMPL

17 SD1FLT1.COMPL

18 SD1FLT2.COMPH SD1FLT2.COMPH_OR_COMPL

19 SD1FLT2.COMPL

20 SD1FLT3.COMPH SD1FLT3.COMPH_OR_COMPL

21 SD1FLT3.COMPL

22 SD1FLT4.COMPH SD1FLT4.COMPH_OR_COMPL

23 SD1FLT4.COMPL

24 SD2FLT1.COMPH SD2FLT1.COMPH_OR_COMPL

25 SD2FLT1.COMPL

26 SD2FLT2.COMPH SD2FLT2.COMPH_OR_COMPL

27 SD2FLT2.COMPL

28 SD2FLT3.COMPH SD2FLT3.COMPH_OR_COMPL

29 SD2FLT3.COMPL

30 SD2FLT4.COMPH SD2FLT4.COMPH_OR_COMPL

31 SD2FLT4.COMPL

MUX 0 1 2 3

0 CMPSS1.CTRIPH CMPSS1.CTRIPH_OR_CTRIPL ADCAEVT1 ECAP1.OUT

1 CMPSS1.CTRIPL INPUTXBAR1 ADCCEVT1

2 CMPSS2.CTRIPH CMPSS2.CTRIPH_OR_CTRIPL ADCAEVT2 ECAP2.OUT

3 CMPSS2.CTRIPL INPUTXBAR2 ADCCEVT2

4 CMPSS3.CTRIPH CMPSS3.CTRIPH_OR_CTRIPL ADCAEVT3 ECAP3.OUT

5 CMPSS3.CTRIPL INPUTXBAR3 ADCCEVT3

6 CMPSS4.CTRIPH CMPSS4.CTRIPH_OR_CTRIPL ADCAEVT4 ECAP4.OUT

7 CMPSS4.CTRIPL INPUTXBAR4 ADCCEVT4

8 CMPSS5.CTRIPH CMPSS5.CTRIPH_OR_CTRIPL ADCBEVT1 ECAP5.OUT

9 CMPSS5.CTRIPL INPUTXBAR5 ADCDEVT1

10 CMPSS6.CTRIPH CMPSS6.CTRIPH_OR_CTRIPL ADCBEVT2 ECAP6.OUT

11 CMPSS6.CTRIPL INPUTXBAR6 ADCDEVT2

12 CMPSS7.CTRIPH CMPSS7.CTRIPH_OR_CTRIPL ADCBEVT3

13 CMPSS7.CTRIPL ADCSOCA ADCDEVT3

14 CMPSS8.CTRIPH CMPSS8.CTRIPH_OR_CTRIPL ADCBEVT4 EXTSYNCOUT

15 CMPSS8.CTRIPL ADCSOCB ADCDEVT4

This block diagram is replicated 8 times

EPwmXbarRegs.register

Note: TRIPLOCK register locks the

configuration for the ePWM X-Bar

Loading...

Loading...