Watchdog Timer

5 - 8 TMS320F2837xD Microcontroller Workshop - System Initialization

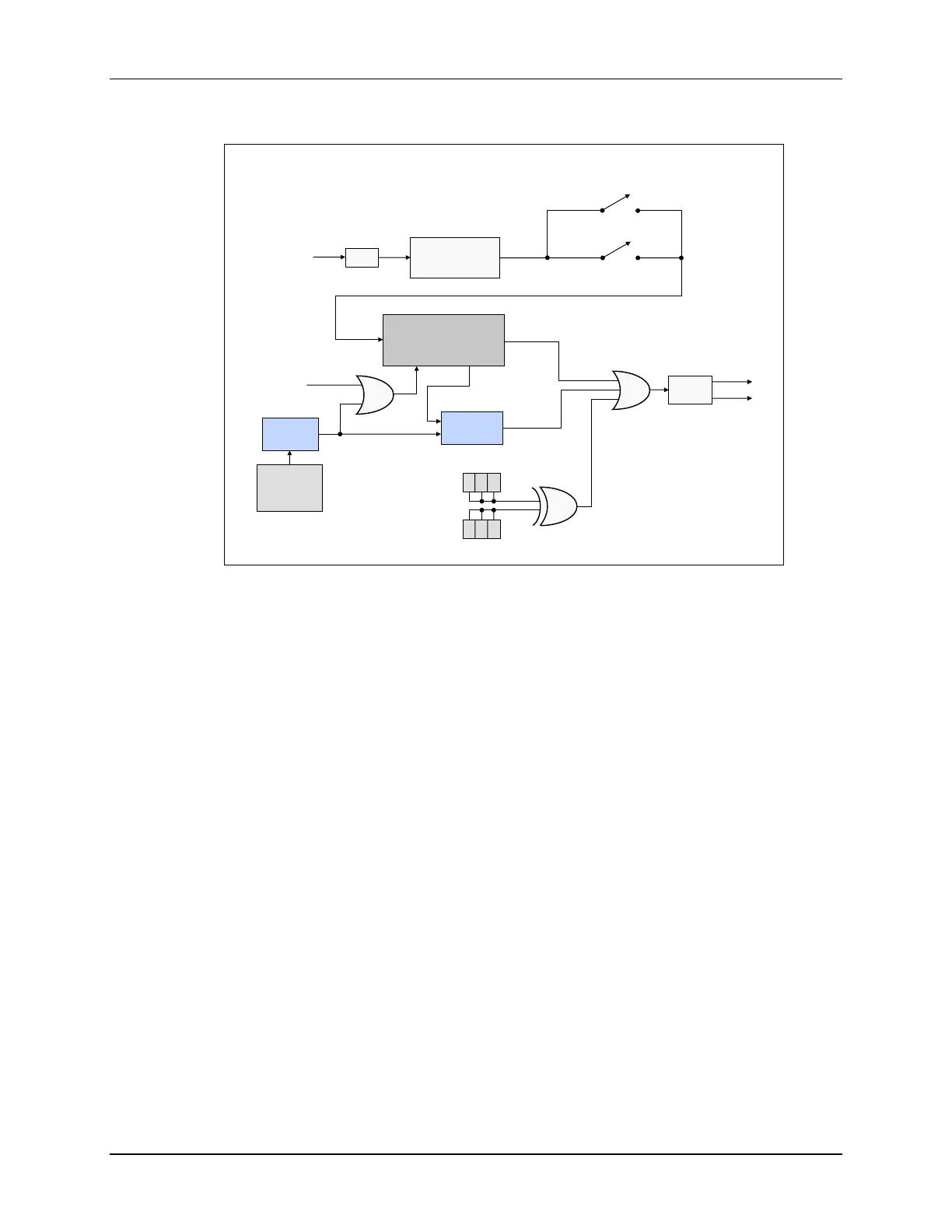

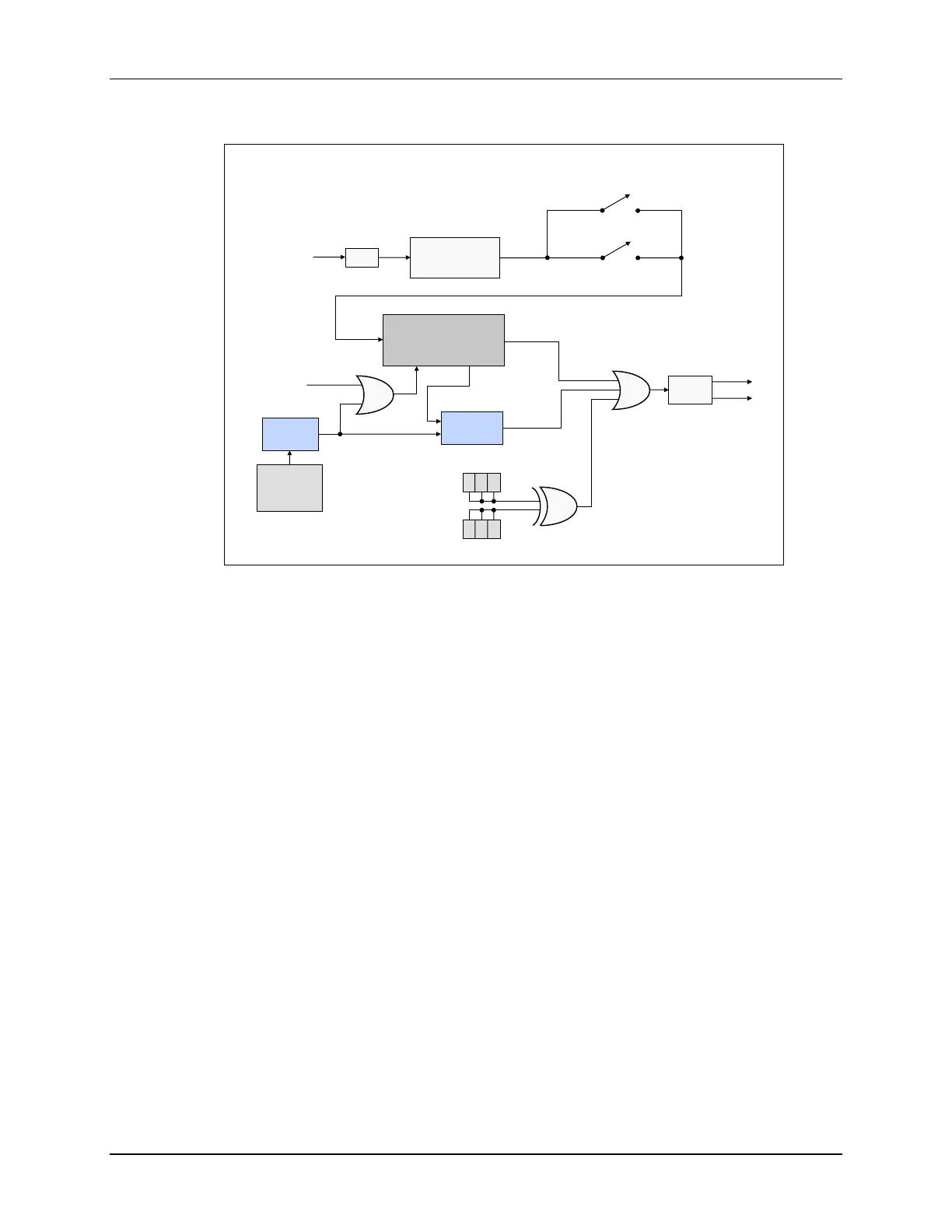

WDCLK

System

Reset

8-bit Watchdog

Counter

CLR

Watchdog

Reset Key

Register

55 + AA

Detector

1 0 1

/

/

3

3

WDDIS

WDCHK

Bad WDCHK Key

/512

Output

Pulse

WDRST

WDINT

WDOVERRIDE

Good Key

Watchdog

Prescaler

WDPS

WDCNTR

window

minimum

WDWCR

WDCNTR

less than

WDWCR

CNT

WDKEY

Watchdog Timer Module

The watchdog clock is divided by 512 and prescaled, if desired for slower watchdog time periods.

A watchdog disable switch allows the watchdog to be enabled and disabled. Also a watchdog

override switch provides an additional safety mechanism to insure the watchdog cannot be

disabled. Once set, the only means to disable the watchdog is by a system reset.

During initialization, a value ‘101’ is written into the watchdog check bit fields. Any other values

will cause a reset or interrupt. During run time, the correct keys must be written into the

watchdog key register before the watchdog counter overflows and issues a reset or interrupt.

Issuing a reset or interrupt is user-selectable. The watchdog also contains an optional

“windowing” feature that requires a minimum delay between counter resets.

Loading...

Loading...