Watchdog Timer

TMS320F2837xD Microcontroller Workshop - System Initialization 5 - 9

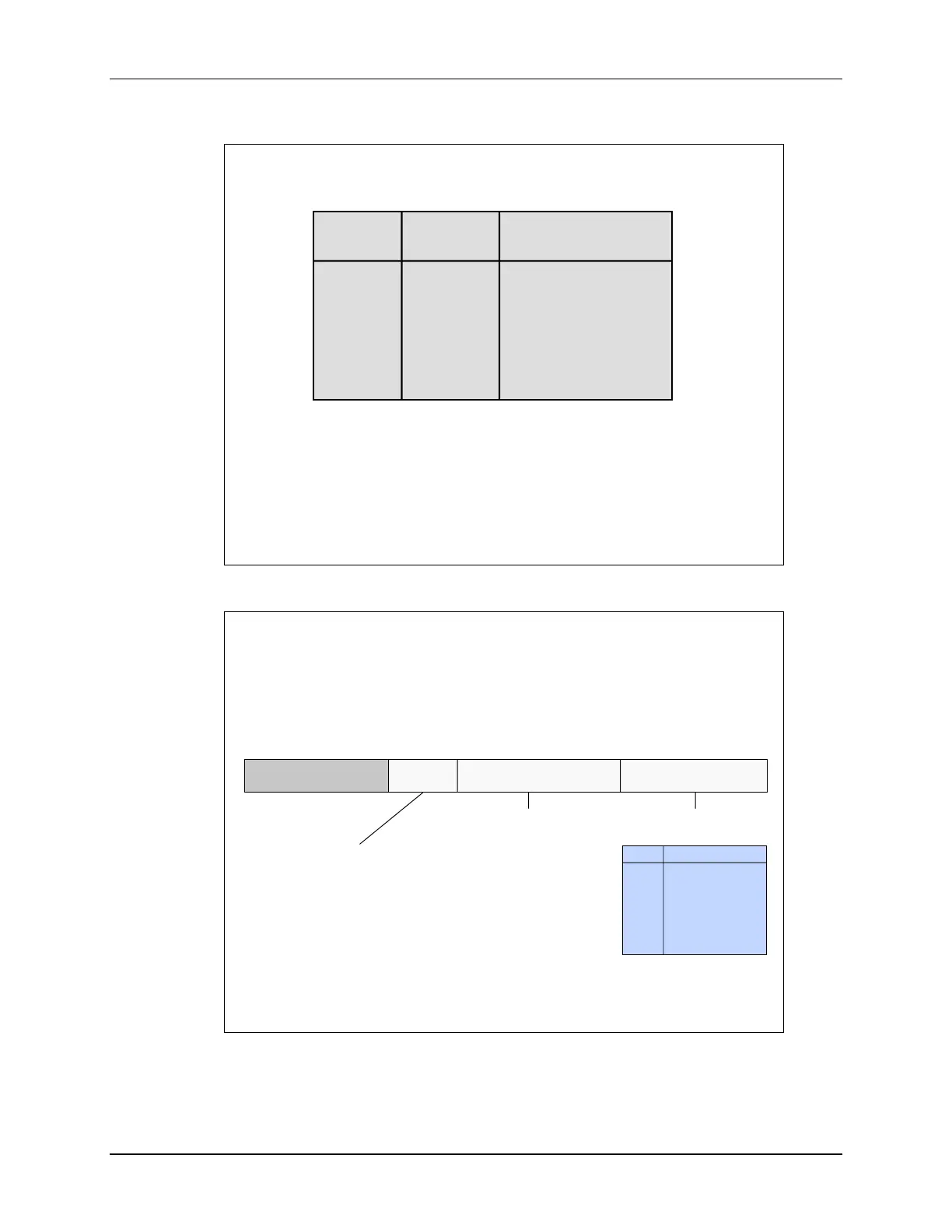

WDPS FRC WD timeout period

Bits rollover @ 10 MHz WDCLK

00x: 1 13.11 ms *

010: 2 26.22 ms

011: 4 52.44 ms

100: 8 104.88 ms

101: 16 209.76 ms

110: 32 419.52 ms

111: 64 839.04 ms

Watchdog Period Selection

Remember: Watchdog starts counting immediately after

reset is released!

Reset default with WDCLK = 10 MHz computed as

(1/10 MHz) * 512 * 256 = 13.11 ms

* reset default

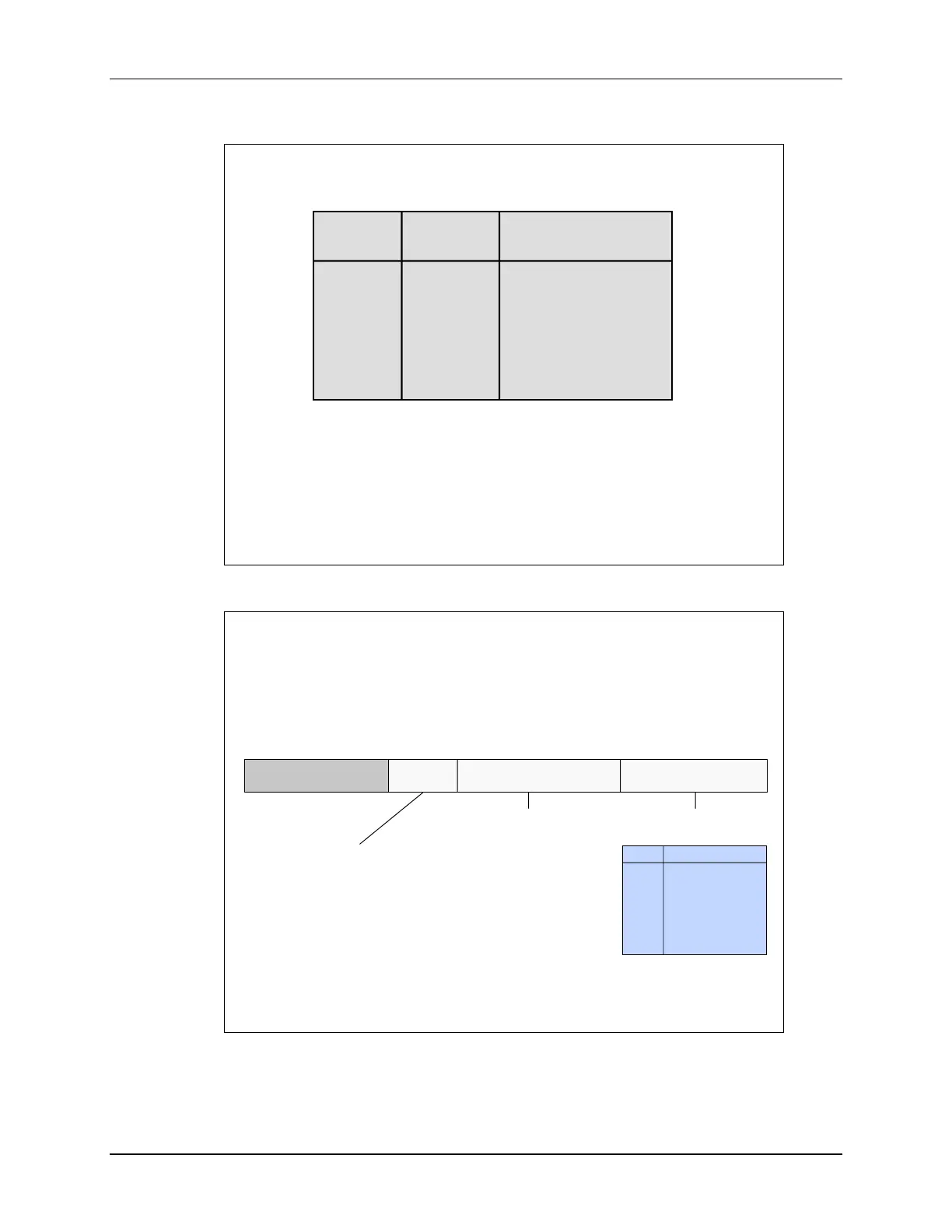

Watchdog Timer Control Register

SysCtrlRegs.WDCR (lab file: Watchdog.c)

WDDIS

6 5 - 3 2 - 0

WDPS

WDCHK

Logic Check Bits

Write as 101 or reset

immediately triggered

WD Prescale

Selection Bits

Watchdog Disable Bit

Write 1 to disable

(Functions only if WD OVERRIDE

bit in SCSR is equal to 1)

reserved

15 - 7

WDPS WDCLK =

0 0 x OSCCLK / 512 / 1

0 1 0 OSCCLK / 512 / 2

0 1 1 OSCCLK / 512 / 4

1 0 0 OSCCLK / 512 / 8

1 0 1 OSCCLK / 512 / 16

1 1 0 OSCCLK / 512 / 32

1 1 1 OSCCLK / 512 / 64

Loading...

Loading...