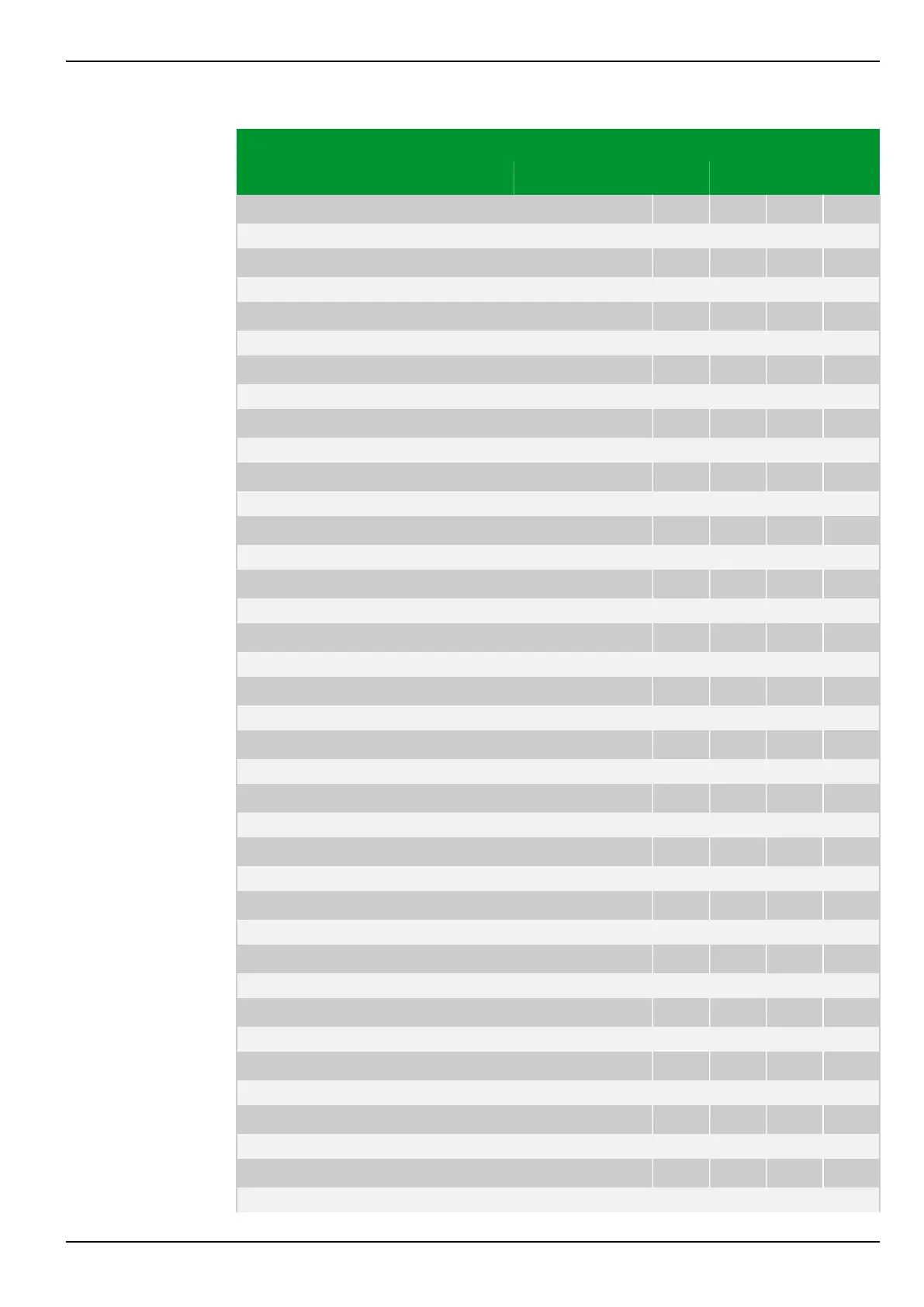

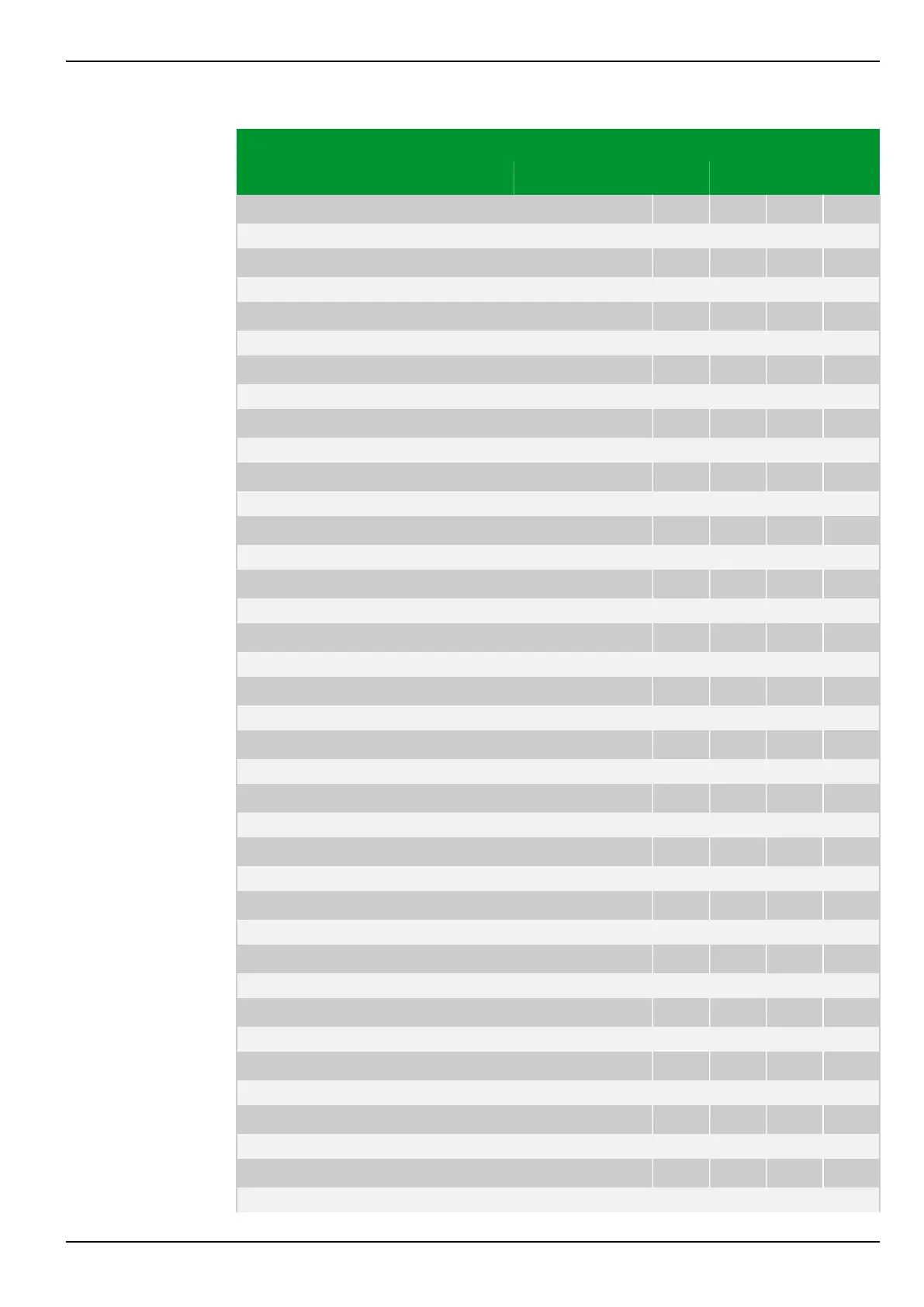

Parameter Address

Default Min Max Unit Logic Diagram

[spacer]

LOGIC: Op. mode t output 70

045 021

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 71

045 025

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 72

045 029

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 73

045 033

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 74

045 037

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 75

045 041

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 76

045 045

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 77

045 049

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 78

045 053

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 79

045 057

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 80

045 061

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 81

045 065

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 82

045 069

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 83

045 073

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 84

045 077

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 85

045 081

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 86

045 085

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 87

045 089

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 88

045 093

0: Without timer stage

7 Settings P634

P634/EN M/R-42-A // P634‑311‑653 7-115

Loading...

Loading...