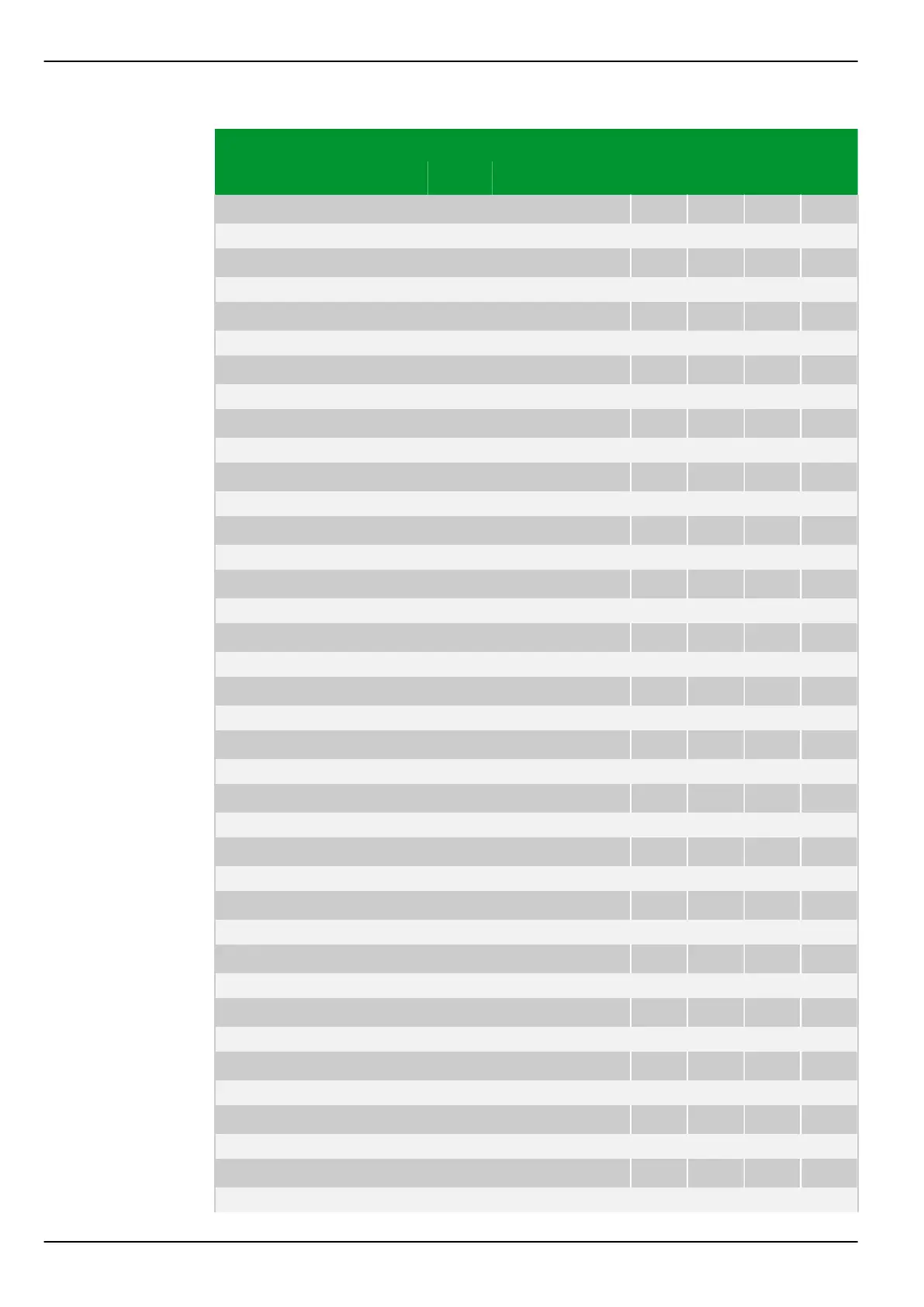

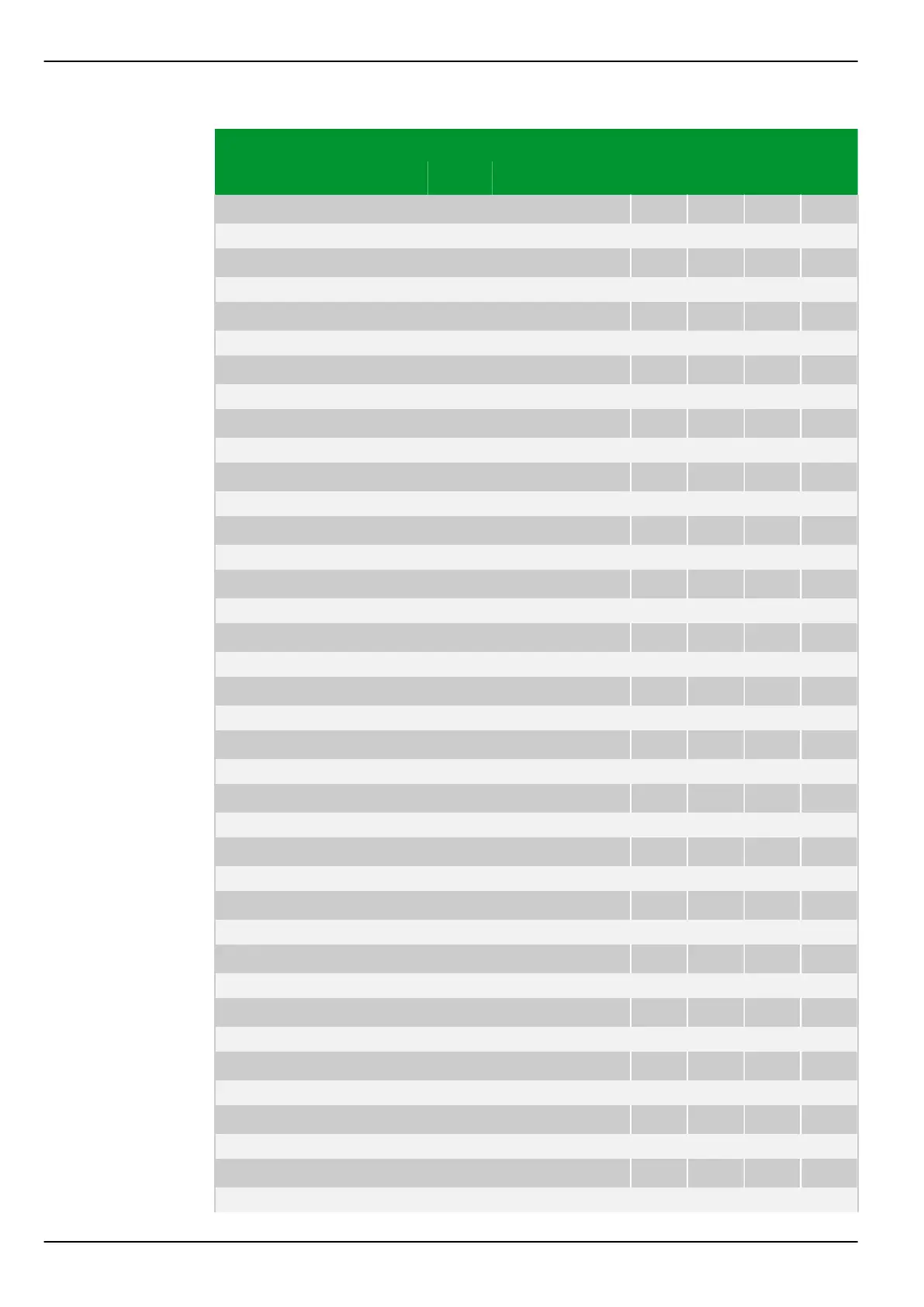

Parameter Address

Default Min Max Unit Logic Diagram

[spacer]

LOGIC: Op. mode t output 89

045 097

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 90

045 101

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 91

045 105

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 92

045 109

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 93

045 113

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 94

045 117

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 95

045 121

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 96

045 125

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 97

045 129

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 98

045 133

0: Without timer stage

[spacer]

LOGIC: Op. mode t output 99

045 137

0: Without timer stage

[spacer]

LOGIC: Op. mode t output100

045 141

0: Without timer stage

[spacer]

LOGIC: Op. mode t output101

045 145

0: Without timer stage

[spacer]

LOGIC: Op. mode t output102

045 149

0: Without timer stage

[spacer]

LOGIC: Op. mode t output103

045 153

0: Without timer stage

[spacer]

LOGIC: Op. mode t output104

045 157

0: Without timer stage

[spacer]

LOGIC: Op. mode t output105

045 161

0: Without timer stage

[spacer]

LOGIC: Op. mode t output106

045 165

0: Without timer stage

[spacer]

LOGIC: Op. mode t output107

045 169

0: Without timer stage

P634 7 Settings

7-116 P634/EN M/R-42-A // P634‑311‑653

Loading...

Loading...