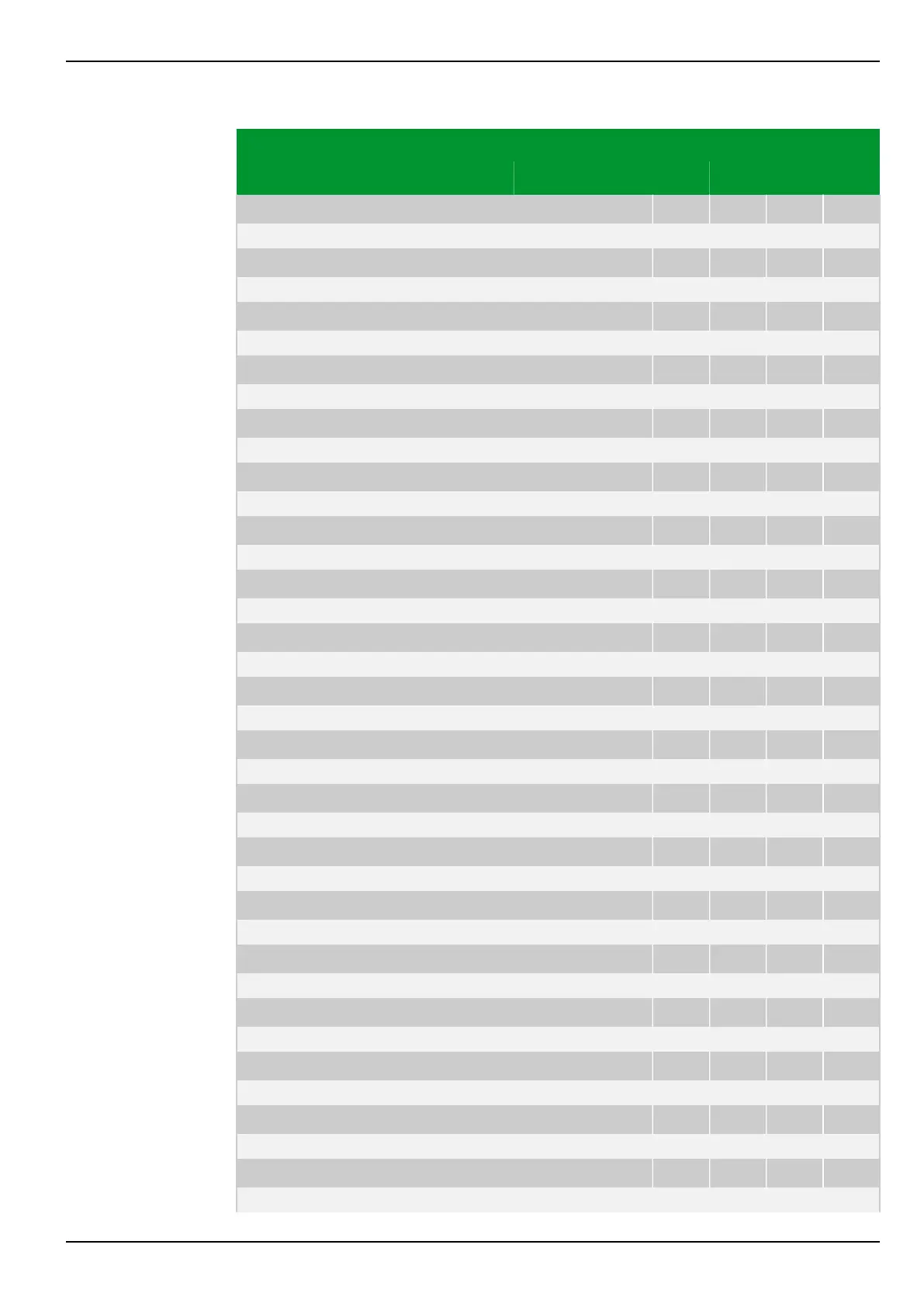

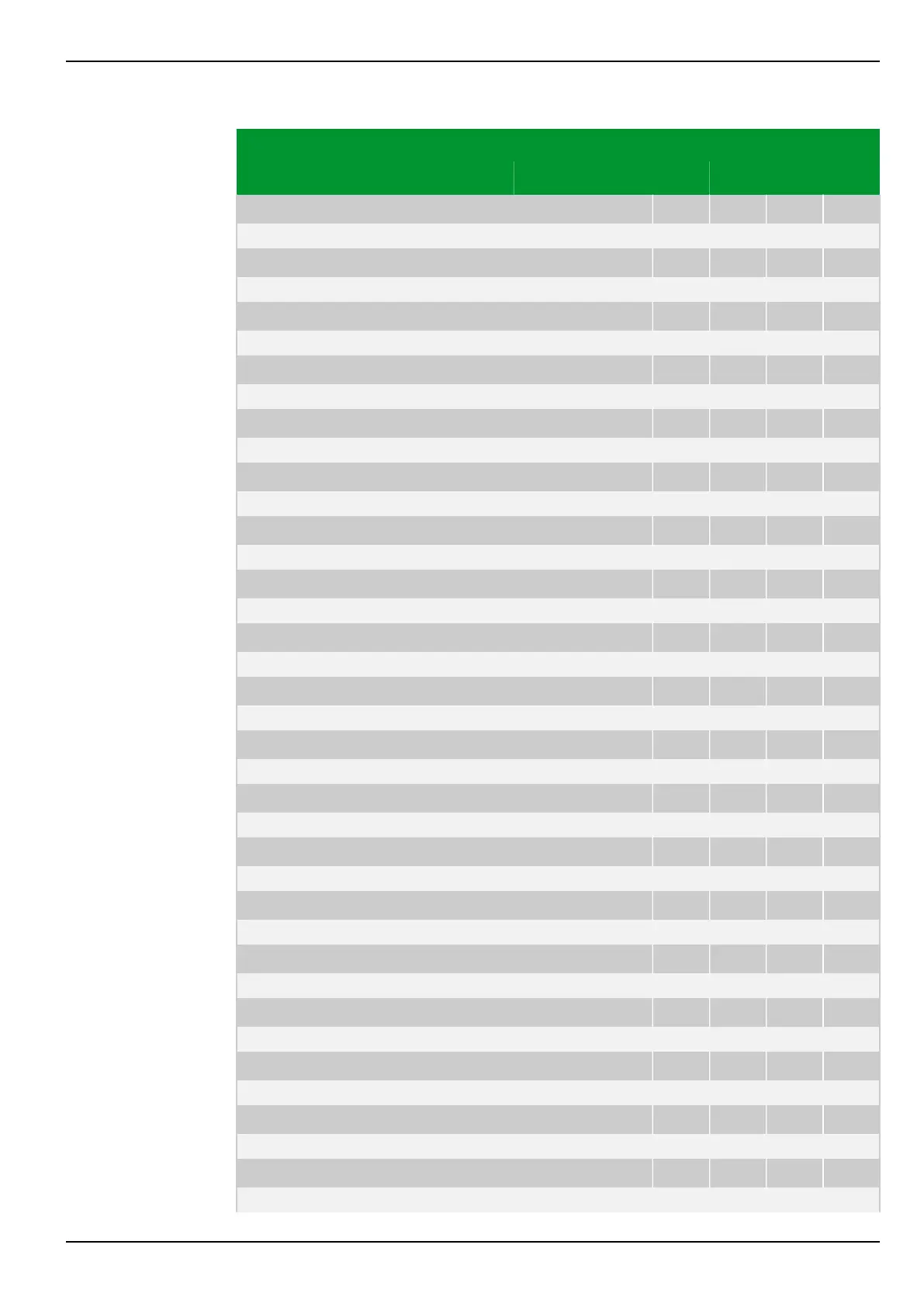

Parameter Address

Default Min Max Unit Logic Diagram

[spacer]

LOGIC: Op. mode t output108

045 173

0: Without timer stage

[spacer]

LOGIC: Op. mode t output109

045 177

0: Without timer stage

[spacer]

LOGIC: Op. mode t output110

045 181

0: Without timer stage

[spacer]

LOGIC: Op. mode t output111

045 185

0: Without timer stage

[spacer]

LOGIC: Op. mode t output112

045 189

0: Without timer stage

[spacer]

LOGIC: Op. mode t output113

045 193

0: Without timer stage

[spacer]

LOGIC: Op. mode t output114

045 197

0: Without timer stage

[spacer]

LOGIC: Op. mode t output115

045 201

0: Without timer stage

[spacer]

LOGIC: Op. mode t output116

045 205

0: Without timer stage

[spacer]

LOGIC: Op. mode t output117

045 209

0: Without timer stage

[spacer]

LOGIC: Op. mode t output118

045 213

0: Without timer stage

[spacer]

LOGIC: Op. mode t output119

045 217

0: Without timer stage

[spacer]

LOGIC: Op. mode t output120

045 221

0: Without timer stage

[spacer]

LOGIC: Op. mode t output121

045 225

0: Without timer stage

[spacer]

LOGIC: Op. mode t output122

045 229

0: Without timer stage

[spacer]

LOGIC: Op. mode t output123

045 233

0: Without timer stage

[spacer]

LOGIC: Op. mode t output124

045 237

0: Without timer stage

[spacer]

LOGIC: Op. mode t output125

045 241

0: Without timer stage

[spacer]

LOGIC: Op. mode t output126

045 245

0: Without timer stage

7 Settings P634

P634/EN M/R-42-A // P634‑311‑653 7-117

Loading...

Loading...