MPC823e Instruction Set—addc

B-8

MPC823e REFERENCE MANUAL

MOTOROLA

INSTRUCTION SET

B

addc

Assembler Syntax addc r

D,

r

A,

rB (OE = 0 Rc = 0)

addc. rD,rA,rB (OE = 0 Rc = 1)

addco rD,rA,rB (OE = 1 Rc = 0)

addco. rD,rA,rB (OE = 1 Rc = 1)

Definition Add Carrying

Operation rD " (rA) + (rB)

Description The sum (rA) + (rB) is placed into rD.

Other registers altered:

❏ Condition Register (CR0 field):

Affected: LT, GT, EQ, SO (if Rc = 1)

If the CR0 field may not reflect the “true” (infinitely

precise) result if overflow occurs (see XER below).

❏ XER:

Affected: CA

Affected: SO, OV (if OE = 1)

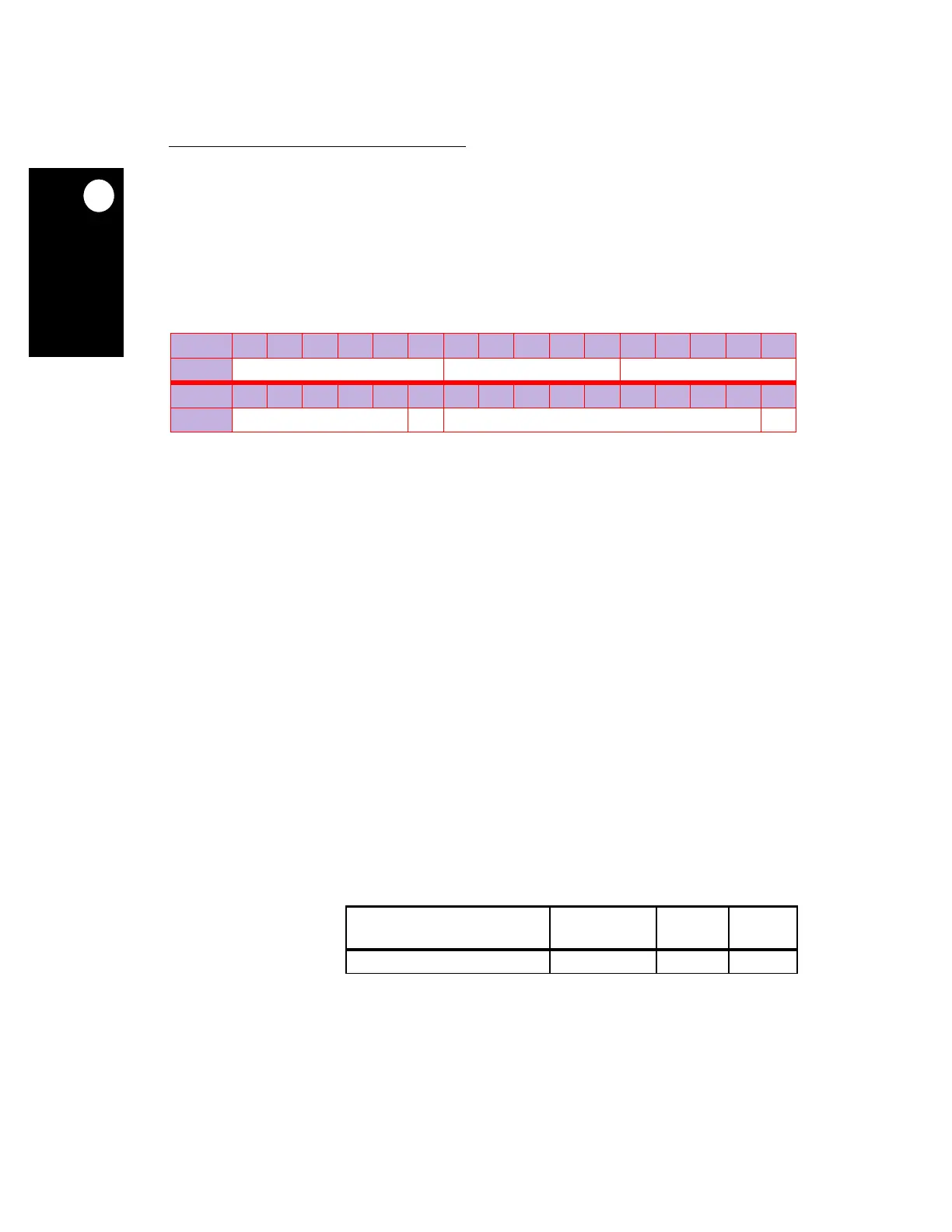

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD 31 D A

BIT 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD BOE 10 RC

POWERPC ARCHITECTURE

LEVEL

SUPERVISOR

LEVEL

OPTIONAL FORM

UISA XO

Loading...

Loading...