Clocks and Power Control

5-18 MPC823e REFERENCE MANUAL MOTOROLA

CLOCKS AND POWER

5

CONTROL

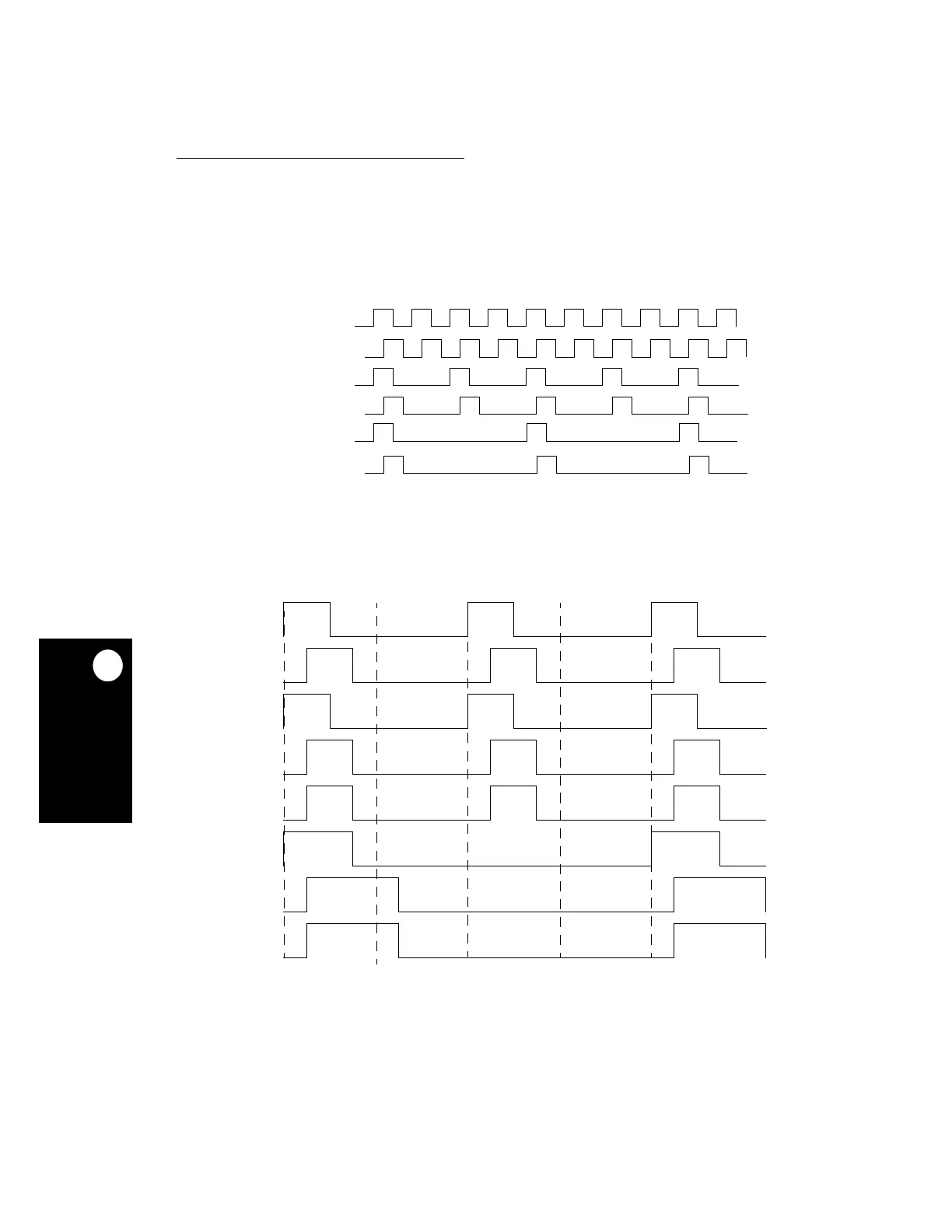

When none of these conditions exist and the CSRC bit of the PLPRCR is set, the general

system clock automatically switches back to low frequency. When the general system clock

is divided, its duty-cycle is modified. One phase remains the same while the other stretches

out. GCLKx and CLKOUT no longer have a 50% duty cycle when the division factor is

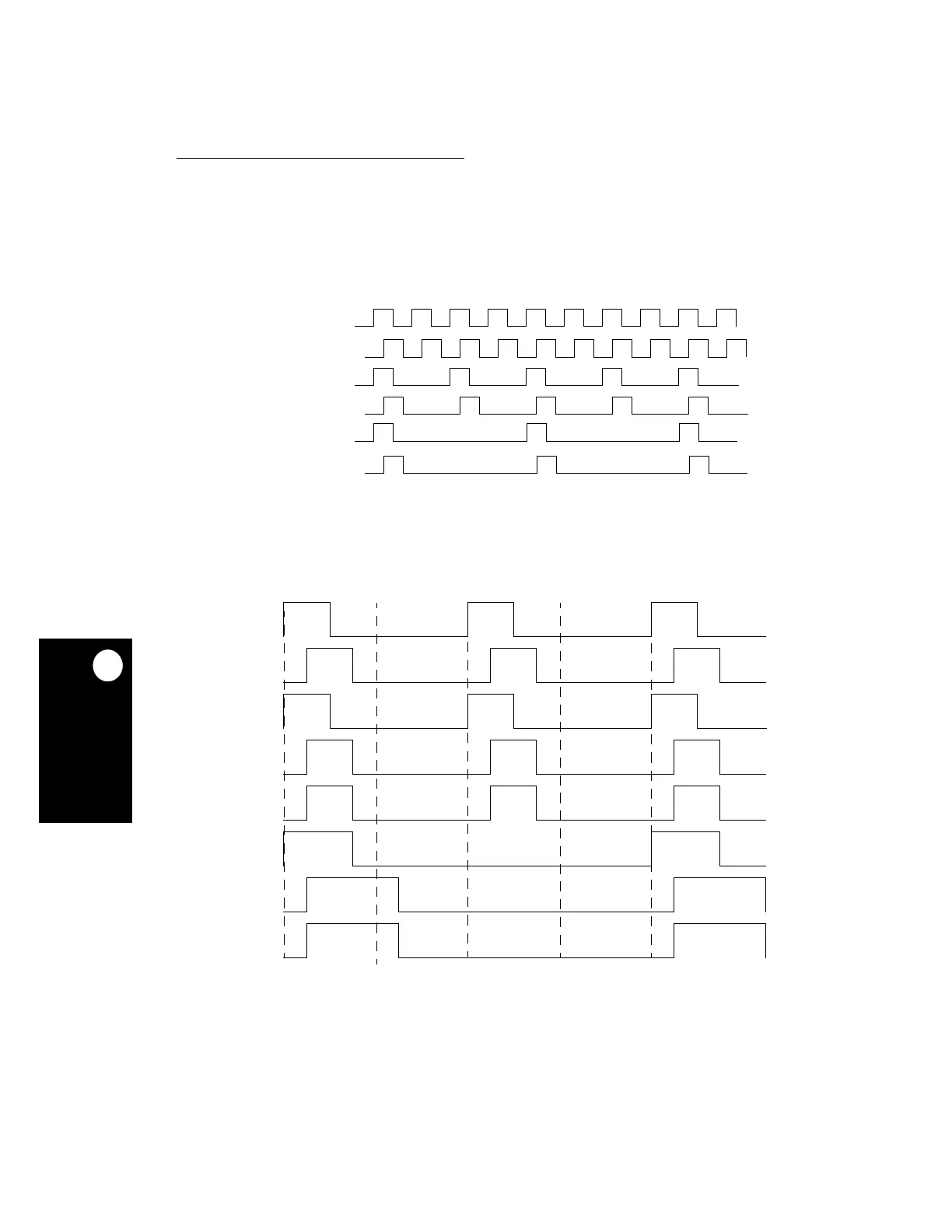

greater than 1, as shown in Figure 5-8 and Figure 5-9.

Figure 5-8. Divided System Clocks Timing Diagram

Figure 5-9. MPC823e Clocks For Division Factor 2

GCLK1 DIVIDED BY 1

GCLK2 DIVIDED BY 1

GCLK1 DIVIDED BY 2

GCLK2 DIVIDED BY 2

GCLK1 DIVIDED BY 4

GCLK2 DIVIDED BY 4

GCLK1

GCLK2

GCLK1_50

GCLK2_50

CLKOUT

GCLK1_50

GCLK2_50

(EBDF=00)

(EBDF=00)

(EBDF=01)

(EBDF=01)

CLKOUT

(EBDF=00)

(EBDF=01)

Loading...

Loading...