Clocks and Power Control

MOTOROLA MPC823e REFERENCE MANUAL 5-19

CLOCKS AND POWER

5

CONTROL

The frequency for the GCLKx system clock is:

The frequency for the GCLKx_50 system clock is:

CLKOUT is derived from GCLK2_50. It defaults to VCOOUT, which is the user-defined

system frequency (25-75MHz). CLKOUT can drive at full-strength, half-strength, or it can be

disabled. The strength of the drive is controlled in the system clock and reset control

register. Disabling or decreasing the strength of CLKOUT reduces power consumption,

noise, and electromagnetic interference on the printed circuit board. When the SPLL is

acquiring lock, the CLKOUT signal is disabled and remains in a low state.

5.3.4.2 THE BAUD RATE GENERATOR CLOCK. The baud rate generator clock

(BRGCLK) is used by the four baud rate generators of the communication processor module

and by the memory controller refresh counter. It defaults to VCOOUT, which is the

user-defined system frequency (25-75MHz). The baud rate generator clock allows the baud

rate generators to continue operating at a fixed frequency, even when the rest of the

MPC823e is operating at a reduced frequency. Refer to Section 16.8 The Baud Rate

Generators for more information about using the baud rate generator clock to save power.

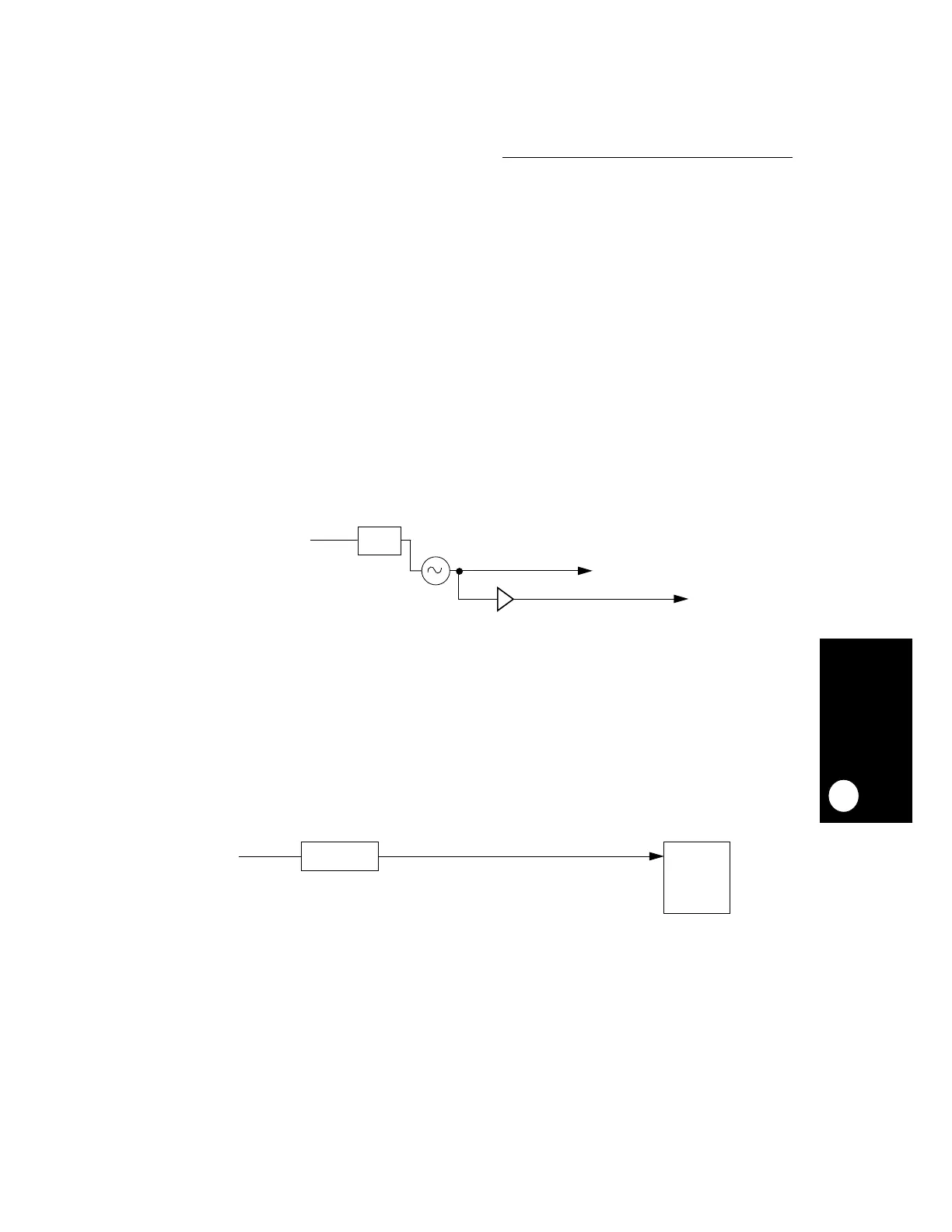

Figure 5-10. CLKOUT Divider

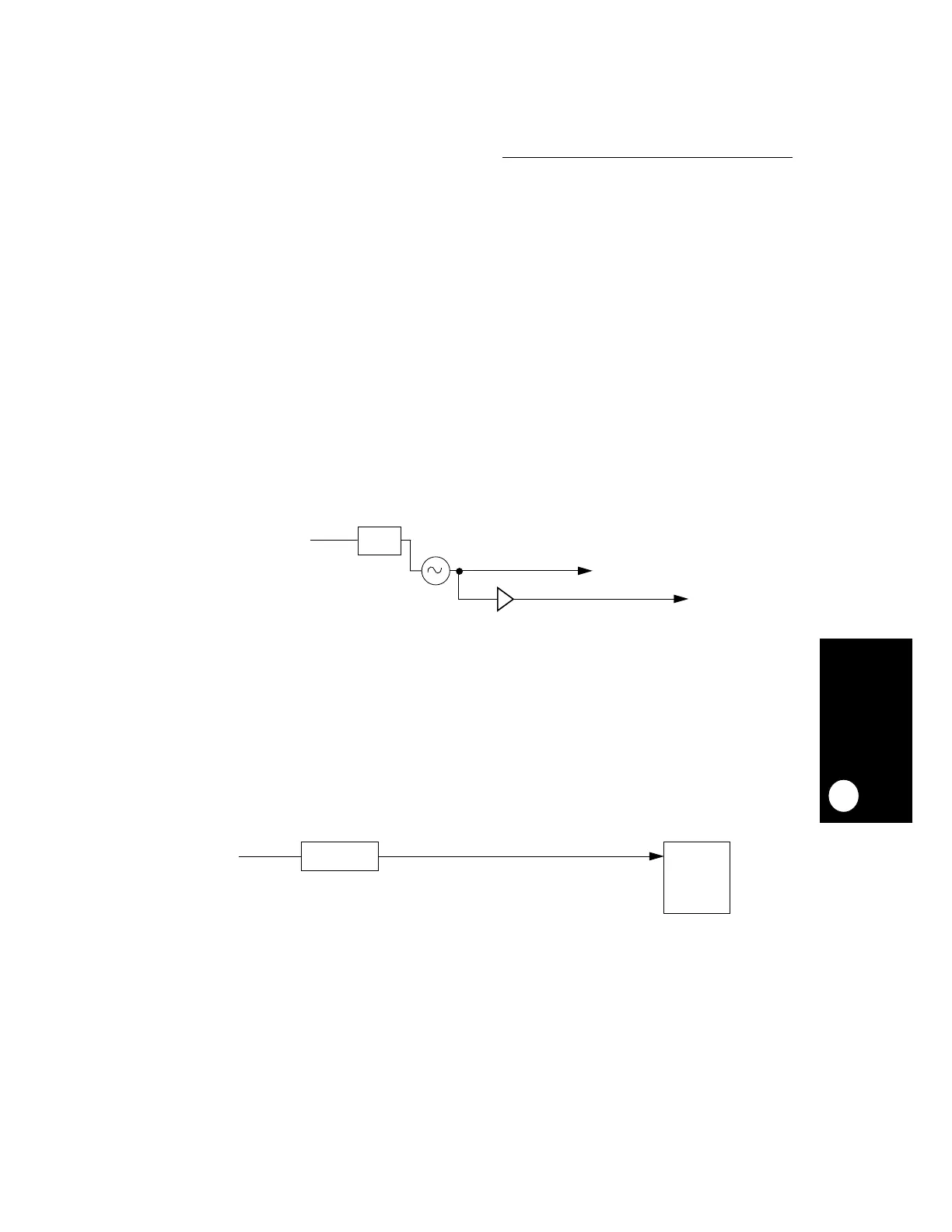

Figure 5-11. BRGCLK Divider

GCLKx

freq

VCOOUT

freq

2

DFNH

()

or 2

DFNL 1+

()

--------------------------------------------------------------=

GCLKx_50

freq

VCOOUT

freq

2

DFNH

()

or 2

DFNL 1+

()

--------------------------------------------------------------

1

EBDF 1+

---------------------------

×

=

EBDF

GCLK2_50

CLKOUT

PHASE

GCLK1

DFBRG

CPM, UPM,

BRGCLK

VCOOUT

(REFRESH

TIMER)

Loading...

Loading...