System Interface Unit

MOTOROLA MPC823e REFERENCE MANUAL 12-33

SYSTEM INTERFACE UNIT

12

MPRE—Multiprocessors Reservation Enable

If this bit is set, then the interprocessor reservation protocol is enabled. The RSV

pin

functions as defined in Section 13.4.10 Storage Reservation Protocol.

0 = RSV

/IRQ2 functions as IRQ2.

1= RSV

/IRQ2 functions as RSV.

MLRC—Multi-Level Reservation Control

This field configures the functionality of the KR

/RETRY/IRQ4/SPKROUT pins.

00 = KR

/RETRY/IRQ4/SPKROUT functions as IRQ4.

01 = KR

/RETRY/IRQ4/SPKROUT is three-stated.

10 = KR

/RETRY/IRQ4/SPKROUT functions as KR/RETRY.

11 = KR

/RETRY/IRQ4/SPKROUT functions as SPKROUT.

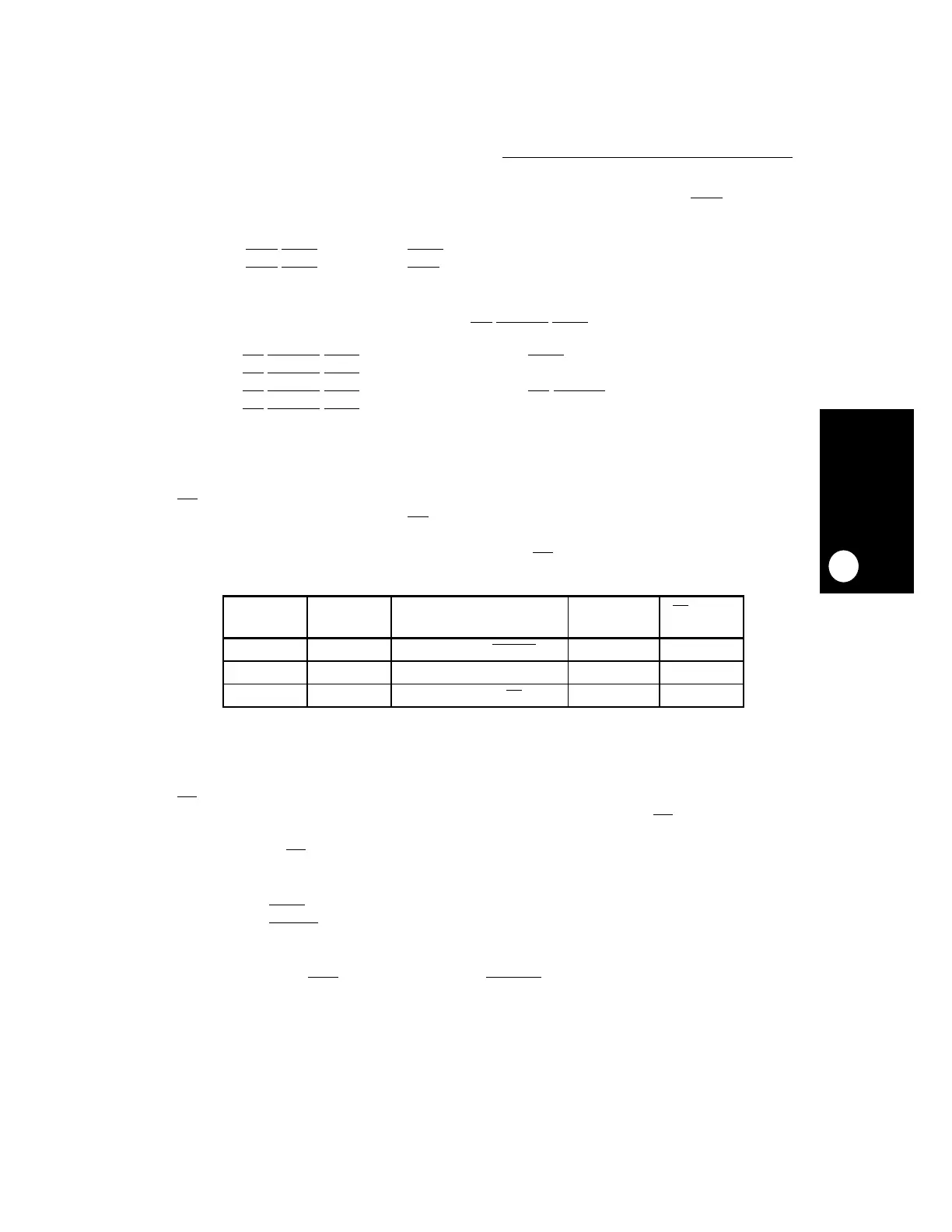

AEME—Asynchronous External Master Enable

This bit configures how the memory controller refers to external asynchronous masters

initiating a transaction. If this bit is set, the memory controller interprets any assertion on the

AS

pin as an external asynchronous master initiating a transaction. If it is reset, the memory

controller ignores the value of the AS

pin. This bit and the GPLA4DIS bit of the machine A

mode register (described in Section 15.3.1.5 Machine A Mode Register) controls the

direction and functionality of the UPWAITA/GPL_A4/AS

pins.

SEME—Synchronous External Master Enable

This bit configures how the memory controller refers to external synchronous masters

initiating a transaction. If this bit is set, the memory controller interprets any assertion on the

TS

pin the external bus does not own as an external synchronous master initiating a

transaction. If it is reset, the memory controller ignores the value of the TS

pin when it does

not own the external bus. When the MPC823e owns the bus, the memory interprets the

assertion of the TS

pin as an internal request.

GB5E—GPL_B5 Enable

0 = The BDIP

functionality is active.

1 = The GPL_B

5 of the memory controller functionality is active.

B2DD—Bank 2 Double Drive

If this bit is set, the CS2

signal is reflected on GPL_x2.

AEME GPLA4DIS PIN USAGE UPWAIT

VALUE

AS VALUE

X 0 Functions as GPL_A4

GND VCC

0 1 Functions as UPWAIT Pin value VCC

1 1 Functions as AS GND Pin value

Loading...

Loading...