Memory Controller

15-66 MPC823e REFERENCE MANUAL MOTOROLA

MEMORY CONTROLLER

15

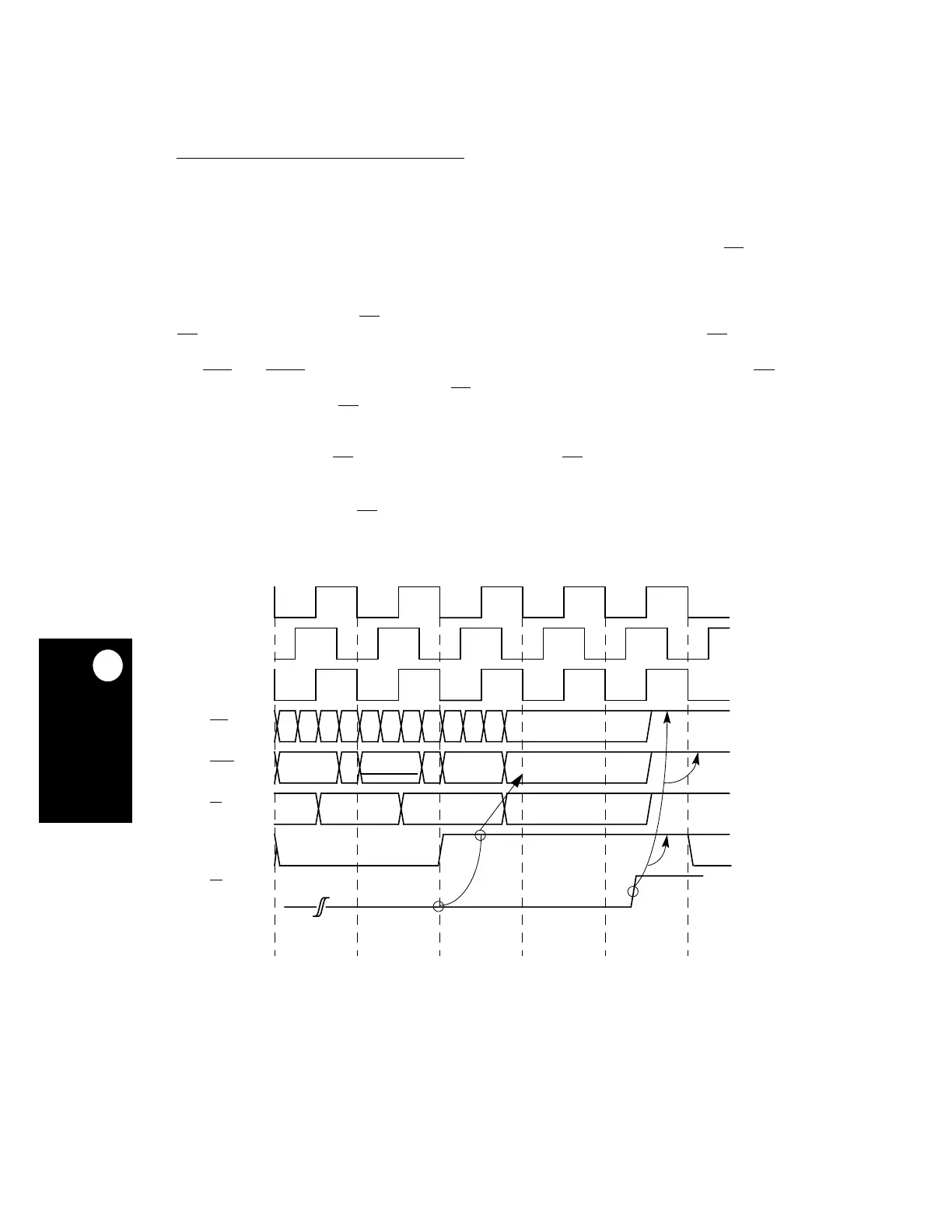

The UPWAITx signal is sampled at the falling edge of the CLKOUT. If the signal is asserted

and the WAEN bit is set in the current RAM word, the UPM is frozen until the UPWAITx

signal is recognized as negated. The value of the external pins driven by the UPM remains

as indicated in the word previously read by the UPM. When the UPWAITx signal is negated,

the UPM continues with its normal functions. Notice that during the wait cycles, the TA

signal

is negated by the UPM.

15.5.5.2 EXTERNAL ASYNCHRONOUS MASTER. The UPM supports asynchronous

external masters using the AS

signal. When you use an external asynchronous master, the

AS

signal behaves like the UPWAITx signal. The UPM enters a wait state if the AS signal is

asserted and the WAEN bit is set in the current RAM word. As illustrated in Figure 15-34,

the CSx

and GPL1 states (C12 and F) and the WAEN value (CC) are frozen until the AS

signal is recognized as deasserted. The TA

signal that is driven by the UPM remains in its

previous value until the AS

signal is negated. The state of the external pins driven by the

UPM remains as indicated in the word previously read by the UPM.

To exit a wait state, the AS

signal must be negated. When AS is negated, all external signals

controlled by the UPM are driven high. The external signals are driven in this state until the

LAST bit is set in a RAM word. The TODT bit of the RAM word is only relevant in the words

read by the UPM after the AS

signal is negated. Refer to Section 15.6 External Master

Support for more information.

Figure 15-34. Wait Mechanism Timing For An External Asynchronous Master

CLKOUT

GCLK1

GCLK2

CSx

GPL1

WAEN

RAM WORD N RAM WORD N+1

A

C1 C2 C3 C4 C5 C6 C7 C8

AS

B C D E F

C9 C10 C11 C12

RAM WORD N+2 WAIT WAIT RAM WORD N+3

TA

AA BB

CC

DD

Loading...

Loading...