Memory Controller

MOTOROLA MPC823e REFERENCE MANUAL 15-65

MEMORY CONTROLLER

15

MEMORY CONTROLLER

15

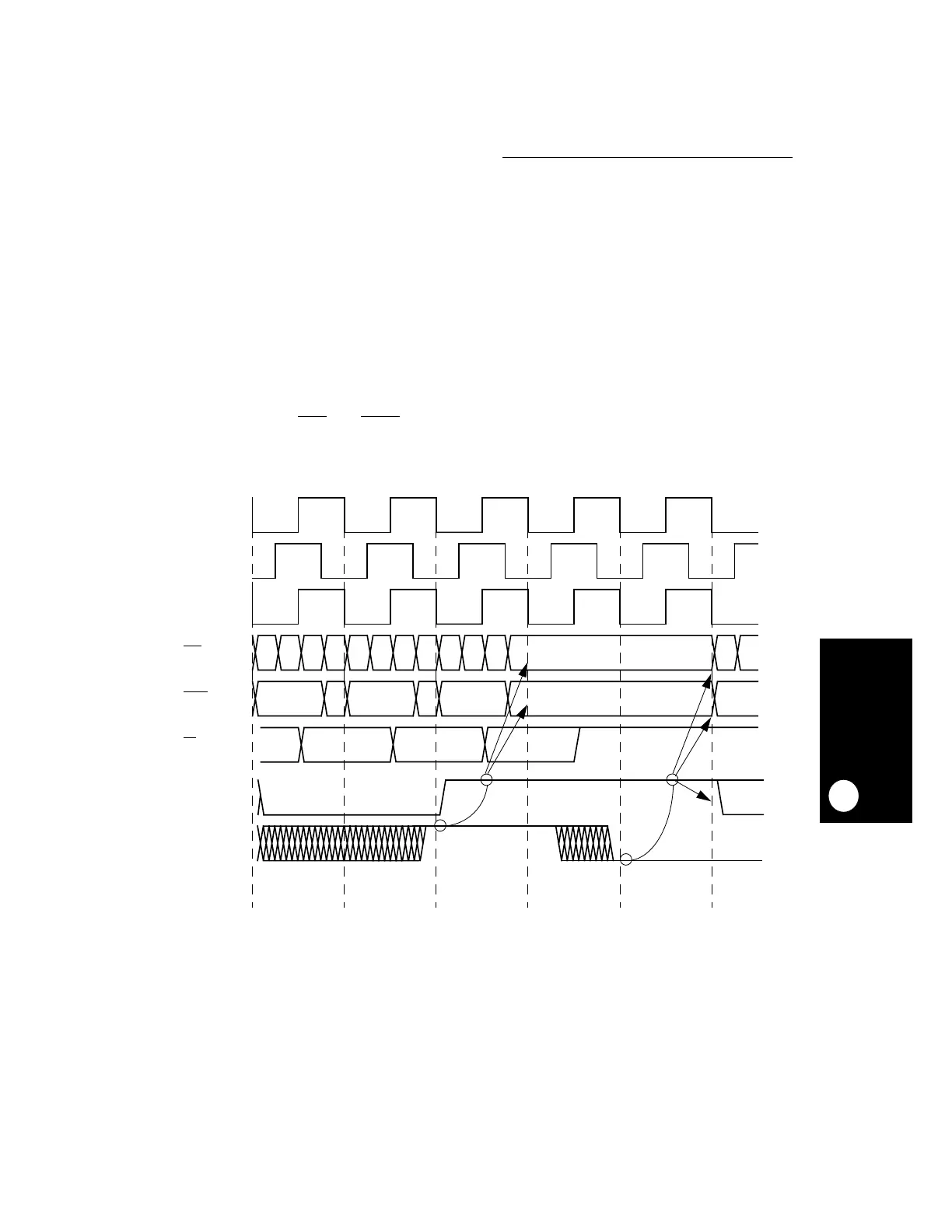

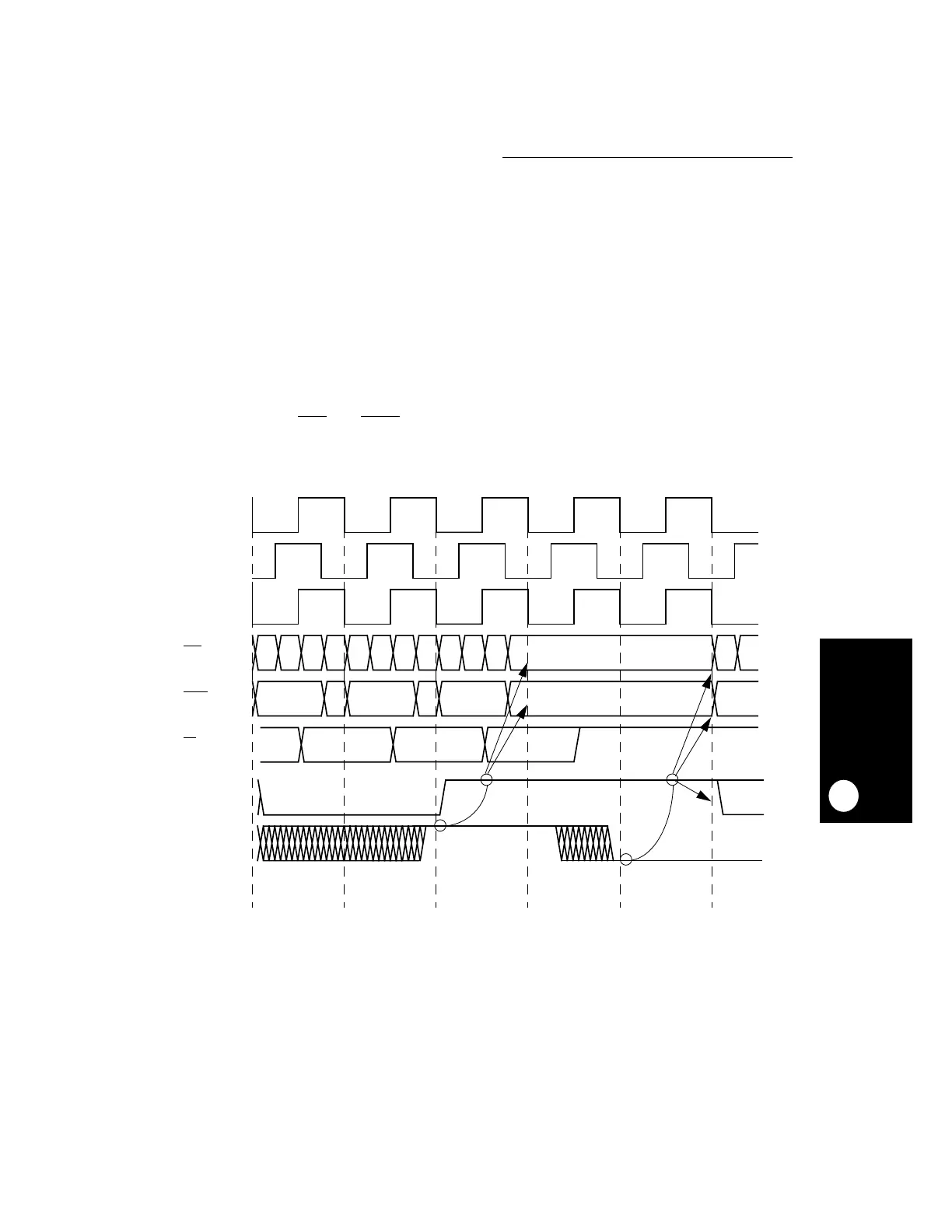

15.5.5 The Wait Mechanism

If the UPM reads a RAM word with the WAEN bit set, the external UPWAITx signal is

sampled and synchronized by the memory controller and the current request is frozen. If the

WAEN bit is asserted, the logical value of the external signals are frozen to the value defined

in the last RAM word accessed and the RAM address increment is disabled until the

UPWAITx signal is negated. This allows wait states to be inserted as required by an external

device through an external signal. A memory disable timer is associated with each UPM.

This timer counts down to zero starting at the value programmed in the DSx field in the

MxMR.

15.5.5.1 INTERNAL AND EXTERNAL SYNCHRONOUS MASTER. Figure 15-33

illustrates how the WAEN bit in the word read by the UPM and the UPWAITx signal is used

to hold the UPM in a particular state until the UPWAITx signal is negated. As illustrated in

Figure 15-33, the CSx

and GPL1 states (C12 and F) and the WAEN value (CC) are frozen

until the UPWAITx signal is recognized as deasserted.

Figure 15-33. Wait Mechanism Timing For Internal and External

Synchronous Masters

CLKOUT

GCLK1

GCLK2

CSx

GPL1

WAEN

RAM WORD N RAM WORD N+1

A

C1 C2 C3 C4 C5 C6 C7 C8

UPWAITx

B C D E F

C9 C10 C11 C12 C13 C14

G

RAM WORD N+2 WAIT WAIT RAM WORD N+3

TA

AA BB

CC

DD

Loading...

Loading...