Memory Controller

MOTOROLA MPC823e REFERENCE MANUAL 15-71

MEMORY CONTROLLER

15

MEMORY CONTROLLER

15

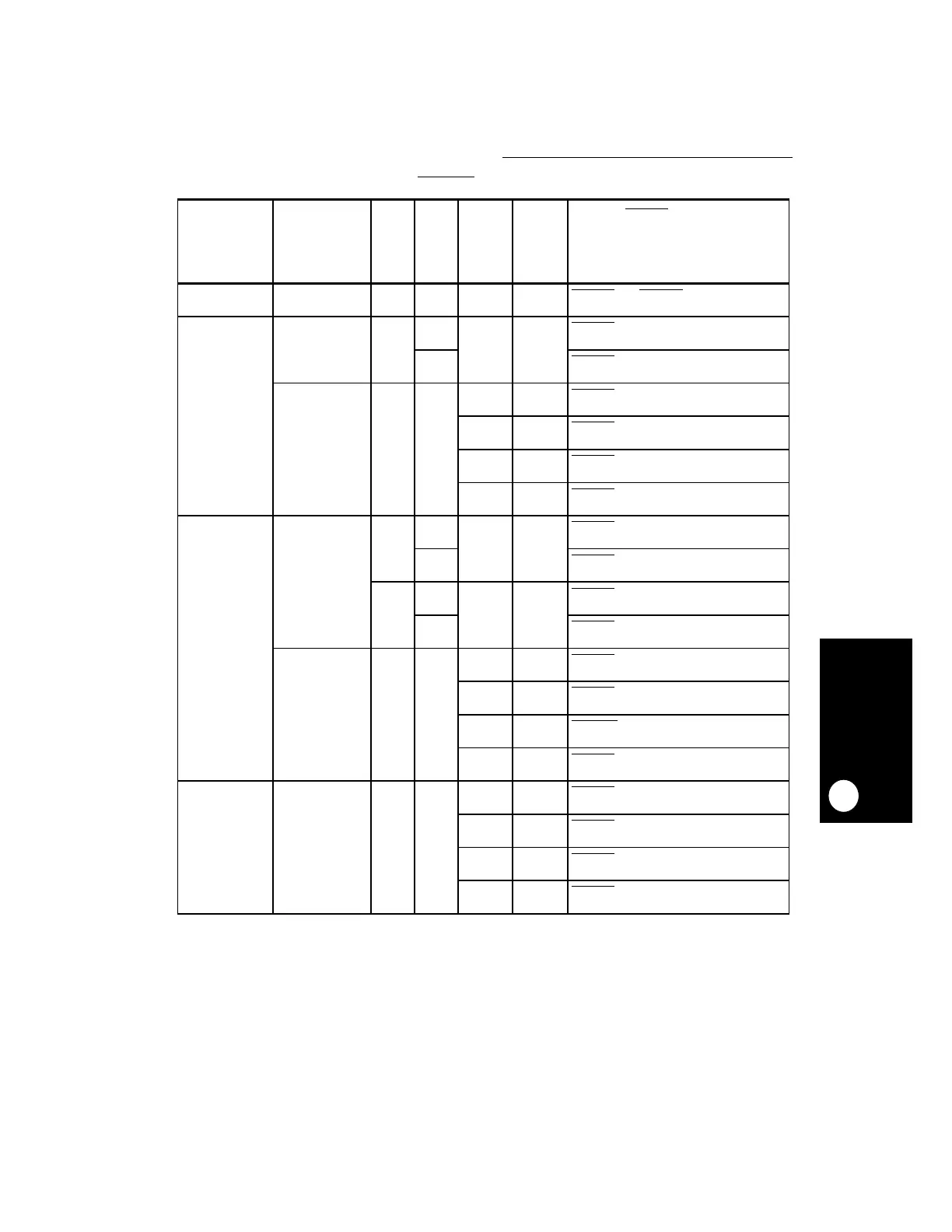

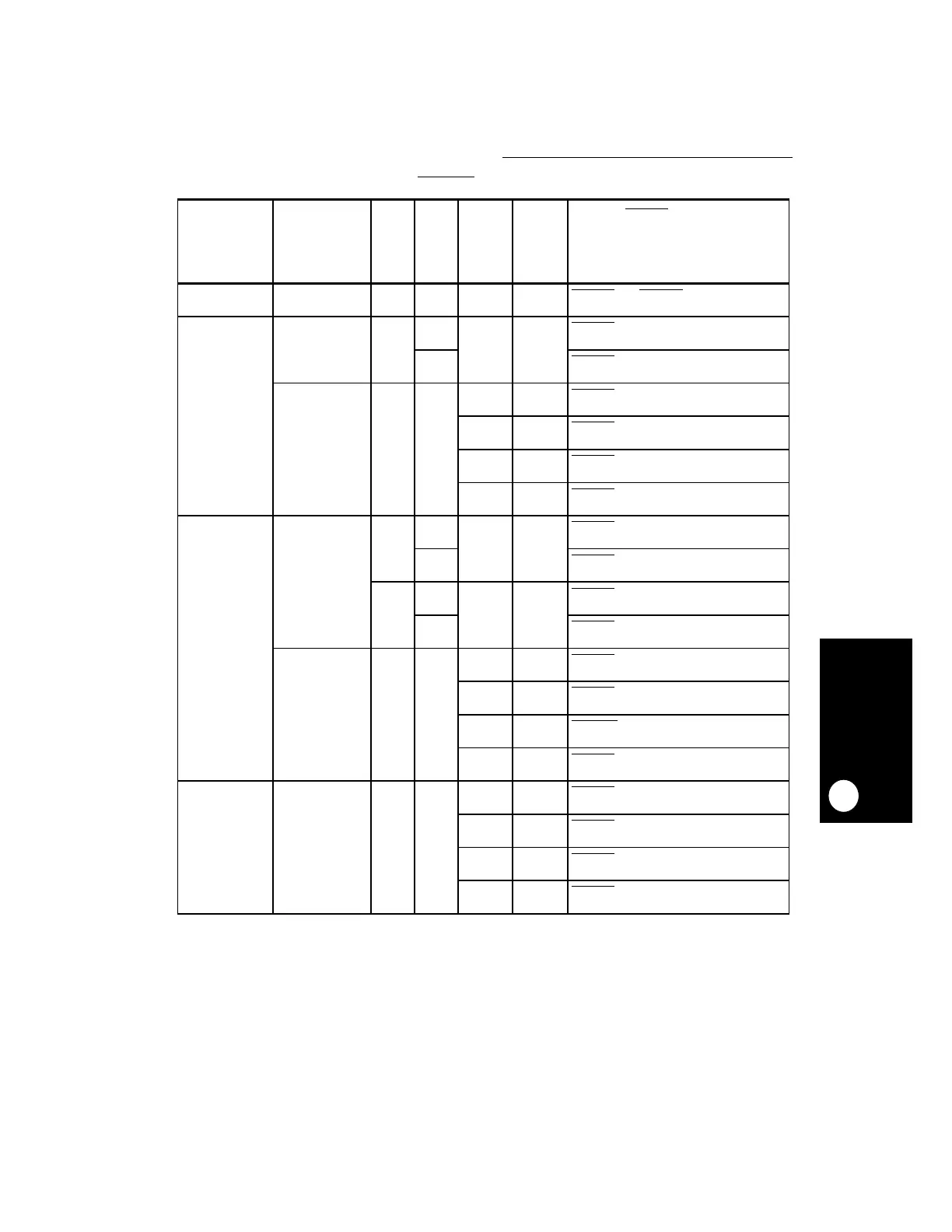

Table 15-9. GPL_x5 Signal (Pin) Behavior

MACHINE

CONTROLLING

THE

MEMORY

ACCESS

MACHINE

CONTROLLING

THE SLAVE

ACCESS

CLOCK CYCLE

G5LA

(ORx)

G5LS

(ORx)

G5T4

(RAM

WORD)

G5T3

(RAM

WORD)

GPL_

x5 BEHAVIOR

AT THE CONTROLLING

CLOCK EDGE

GPCM x N/A N/A x x GPL_A5

and GPL_B5 do not change their

value.

UPMA First x 0 x x GPL_A5

is driven low at the falling edge of

GCLK1.

1 GPL_A5

is driven high at the falling edge

of GCLK1.

Second, Third... x x 0 x GPL_A5

is driven low at the falling edge of

GCLK2 in the current UPM cycle.

1 x GPL_A5

is driven high at the falling edge

of GCLK2 in the current UPM cycle.

x 0 GPL_A5

is driven low at the falling edge of

GCLK1 in the current UPM cycle.

x 1 GPL_A5

is driven high at the falling edge

of GCLK1 in the current UPM cycle.

UPMB First 0 0 x x GPL_B5

is driven low at the falling edge of

GCLK1.

1 GPL_B5

is driven high at the falling edge

of GCLK1.

1 0 x x GPL_A5

is driven low at the falling edge of

GCLK1.

1 GPL_A5

is driven high at the falling edge

of GCLK1.

Second, Third... 0 x 0 x GPL_B5

is driven low at the falling edge of

GCLK2 in the current UPM cycle.

1 x GPL_B5

is driven high at the falling edge

of GCLK2 in the current UPM cycle.

x 0 GPL_B5

is driven low at the falling edge of

GCLK1 in the current UPM cycle.

x 1 GPL_B5

is driven high at the falling edge

of GCLK1 in the current UPM cycle.

UPMB Second, Third... 1 x 0 x GPL_A5

is driven low at the falling edge of

GCLK2 in the current UPM cycle.

1 x GPL_A5

is driven high at the falling edge

of GCLK2 in the current UPM cycle.

x 0 GPL_A5

is driven low at the falling edge of

GCLK1 in the current UPM cycle.

x 1 GPL_A5

is driven high at the falling edge

of GCLK1 in the current UPM cycle.

Loading...

Loading...