Memory Controller

15-70 MPC823e REFERENCE MANUAL MOTOROLA

MEMORY CONTROLLER

15

To connect to external memory devices that require address multiplexing, use the GPL_x5

pin. The state of the GPL_x5

signal logic value depends on the configuration defined in

Table 15-9. The GPL_x5

pin reflects the value of the G5LS bit of the corresponding option

register in the first clock cycle of the slave device access. In subsequent clock cycles, the

state of GPL_x5

is determined by the G5T4 and G5T3 bits in the RAM word. If the UPMB

controls the slave access, you can use the G5LA bit of the option register to select the active

GPL_x5

signal. G5LS only applies to memory requests and not RAM words executed by

internal/external software, exception, or memory periodic timer requests.

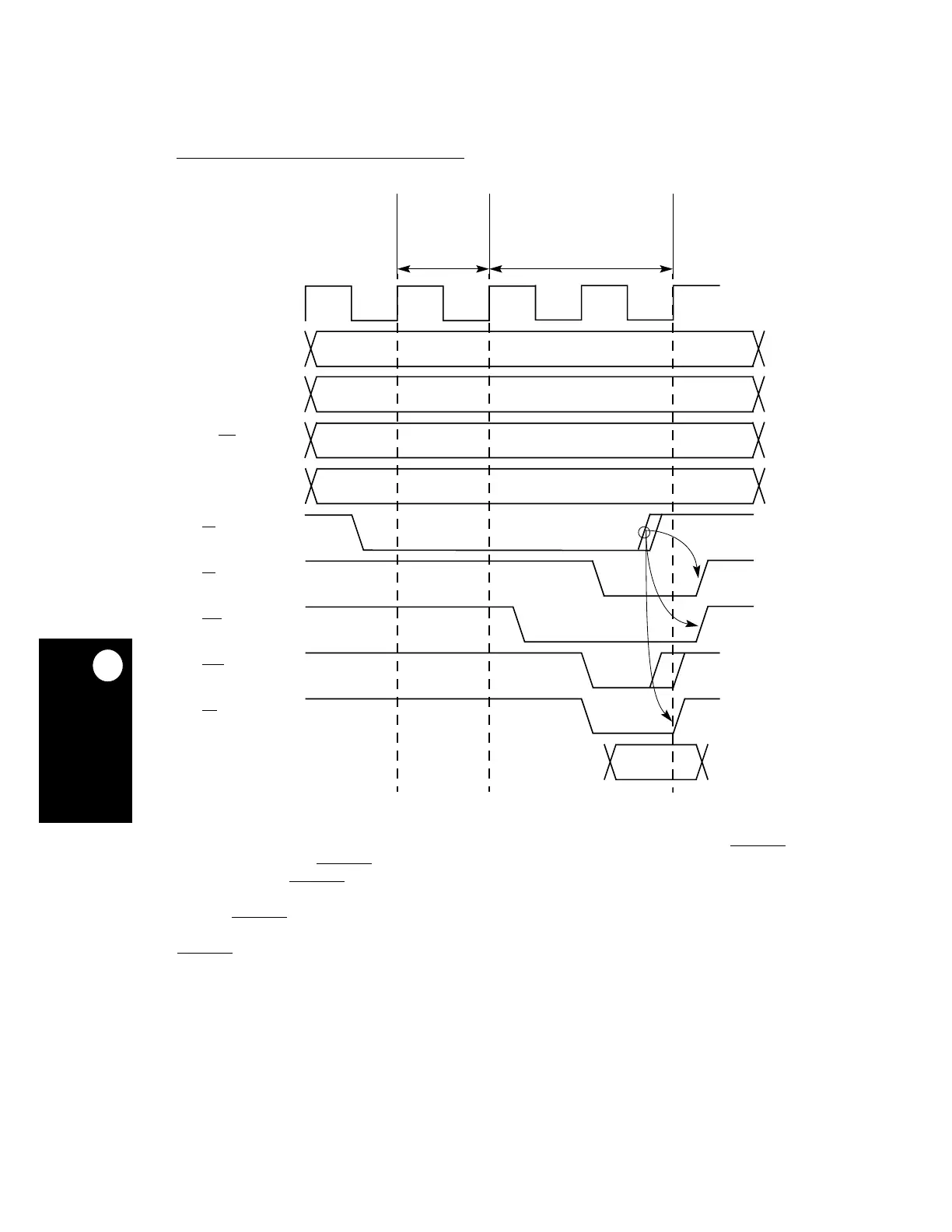

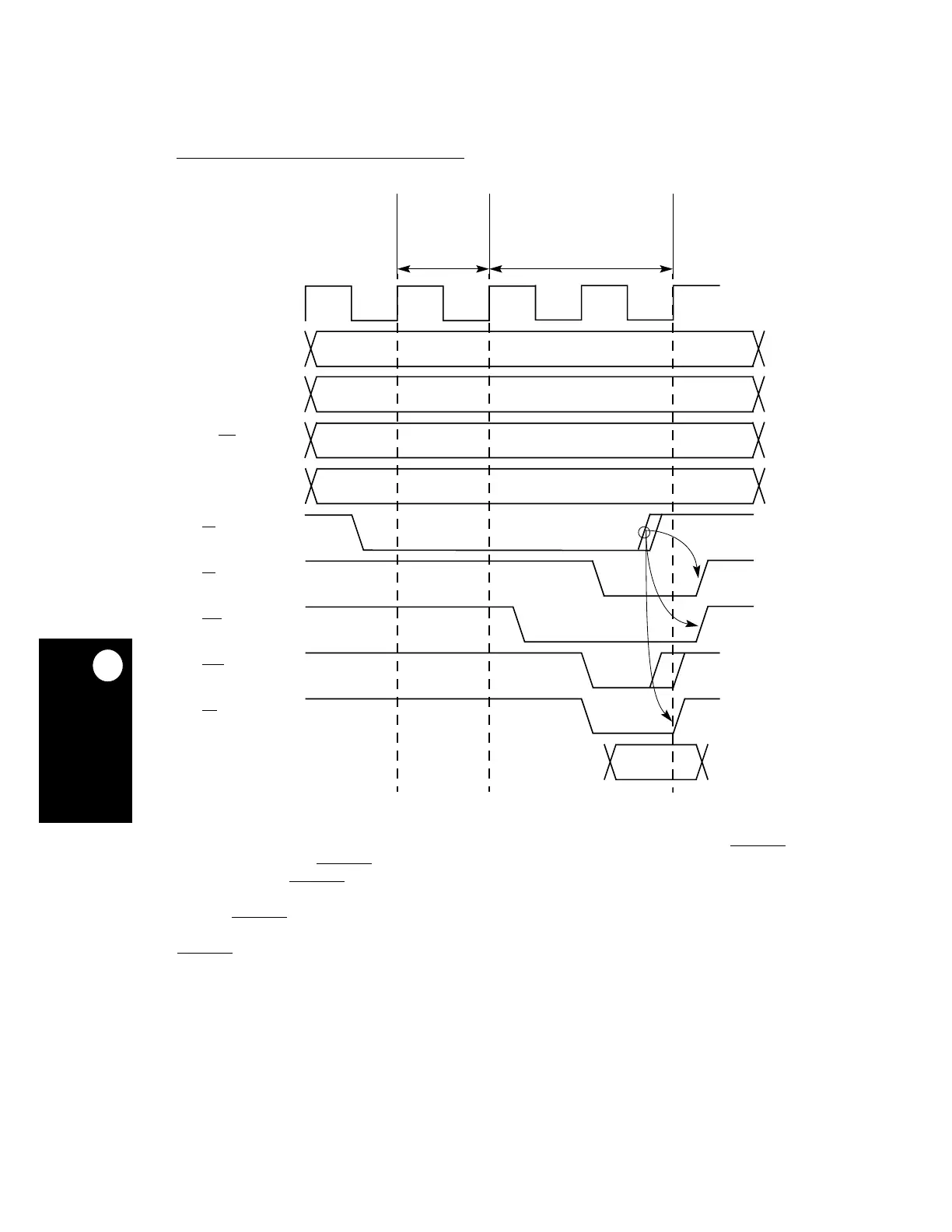

Figure 15-36. Asynchronous External Master Access

CLKOUT

A[6:27]

CSx

WEx

OE

DATA

AS

TA

ADDRESS

MATCH

AND

COMPARE

MEMORY

DEVICE

ACCESS

RD/

WR

TSIZEx

A[28:31]

Loading...

Loading...