Memory Controller

MOTOROLA

MPC823e REFERENCE MANUAL

15-77

MEMORY CONTROLLER

15

MEMORY CONTROLLER

15

3. Translate the timing diagrams into RAM words for each type of memory access. The

bottom half of the figures represent the RAM array contents that handle each of the

possible cycles and each column represents a different word in the RAM array. A

blank cell in each figure indicates a “don’t care” bit, which is typically programmed to

logic 1 to conserve power.

4. Define the UPMA (or UPMB) parameters that control the memory system in the

following sequence. For additional details, see Table 15-10.

— Program the RAM array using the memory command register (MCR) and

memory data register (MDR). The RAM word must be written into the MDR

before you issue the

WRITE

command to the MCR. Repeat this step for all RAM

word entries.

— Initialize the option and base registers of the specific bank according to the

address mapping of the DRAM device you have chosen.

— Use the MS field of the option register to select the machine you have chosen

to control the cycles. Notice that the SAM bit in the option register determines

address multiplexing for the first clock cycle and subsequent cycles are

controlled by the UPM RAM words. Also notice that the AMX field in the UPM

RAM word controls the address multiplexing for the next clock cycle rather than

the current cycle.

— Program the MAMR to select the number of columns and refresh timer

parameters.

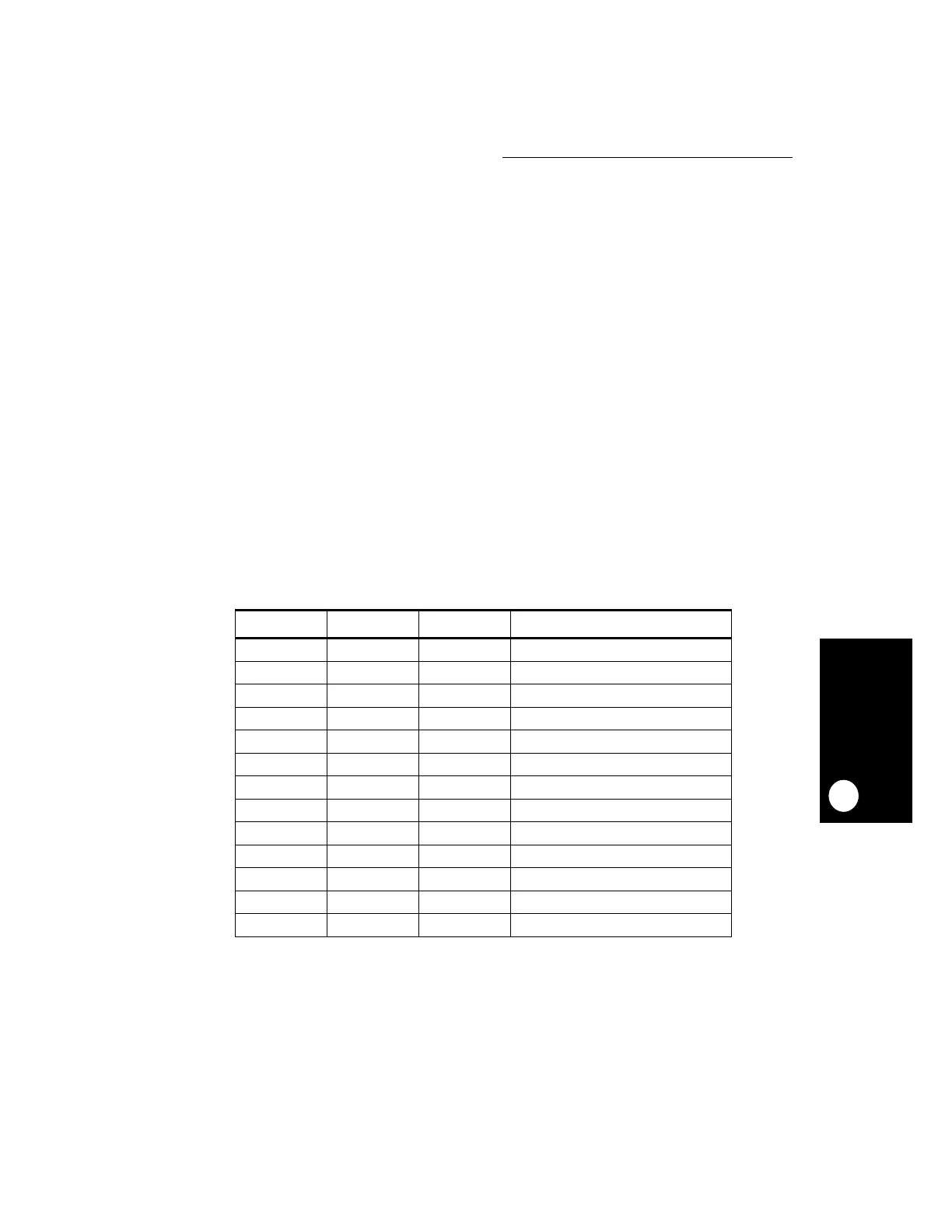

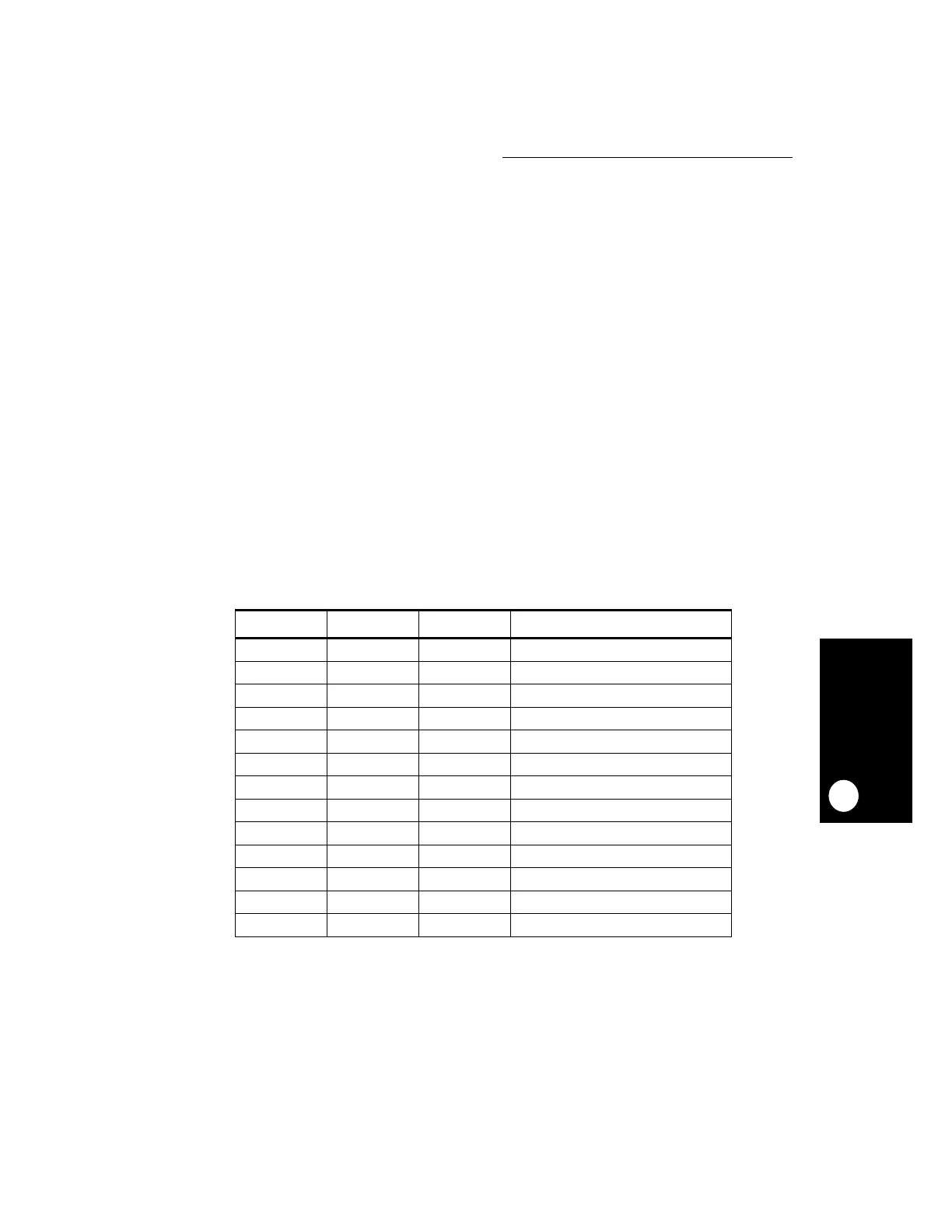

Table 15-10. UPMA Register Settings

FIELD REGISTER VALUE COMMENTS

MS BR1 10 Selects UPMA

PS BR1 00 Selects 32-Bit Bus Width

WP BR1 0 Allows Read and Write Accesses

PTP MPTPR 00000010 Prescaler Divided by Two

PTA MAMR 00001100 15.6

µ

s at a 25MHz Clock

PTAE MAMR 1 Enables Periodic Timer A

AMA MAMR 001 Selects Nine Column Address Pins

DSA MAMR 01 Selects Two Disable Timer Clock Cycles

GPLA4DIS MAMR 0 Disables the UPWAITA Signal

RLFA MAMR 0011 Selects Three Loop Iterations for Read

WLFA MAMR 0011 Selects Three Loop Iterations for Write

SAM OR1 1 Selects Column Address on First Cycle

BI OR1 0 Supports Burst Accesses

Loading...

Loading...