Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-23

RISC

COMMUNICATION

16

PROCESSOR MODULE

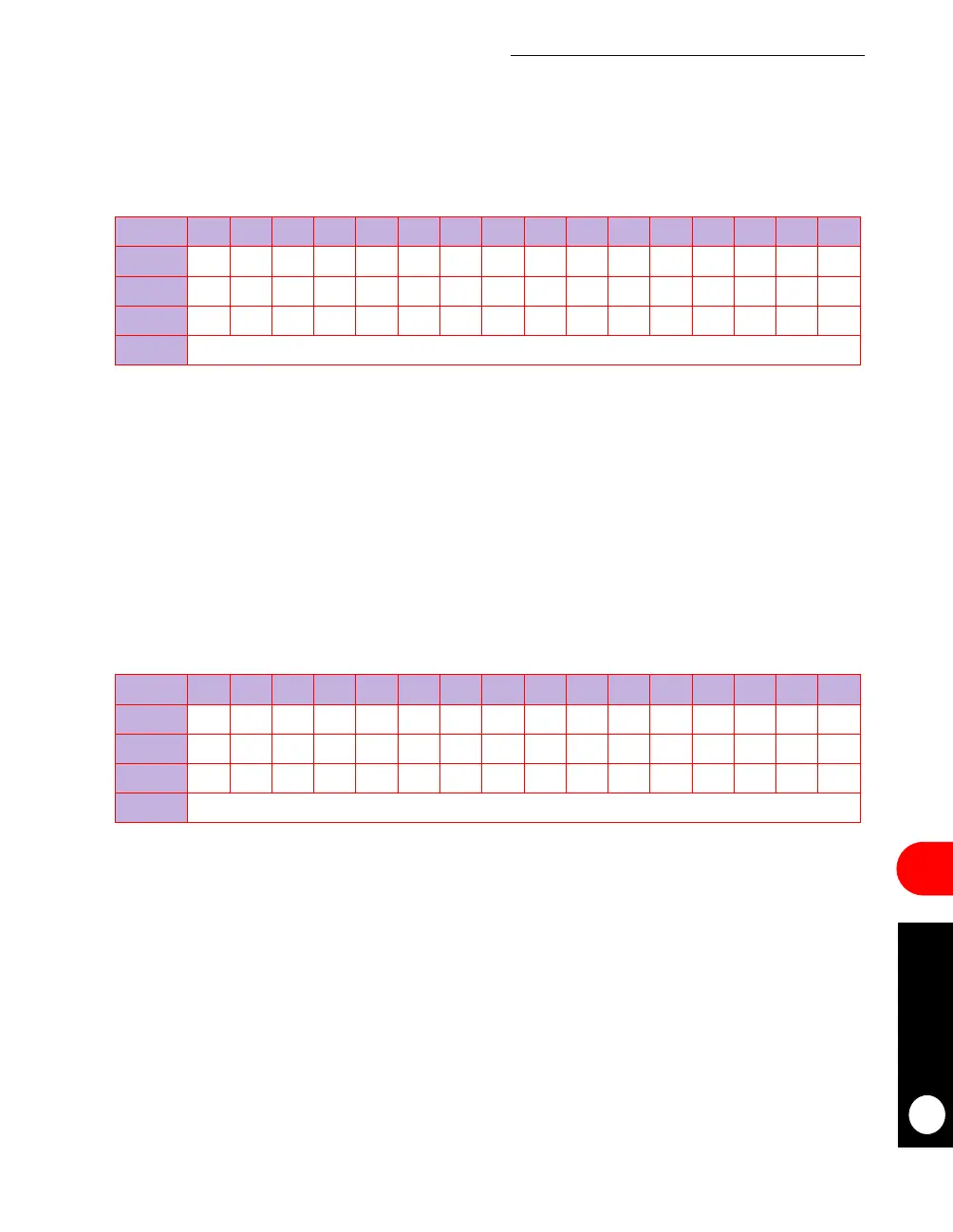

16.2.6.5 RISC TIMER EVENT REGISTER. The 16-bit RISC timer event register (RTER) is

used to report events recognized by the 16 timers and to generate interrupts. However, an

interrupt is only generated if the RISC timer table bit is set in the CPM interrupt mask

register. More than one bit can be cleared once.

TMR0–15—Timer 0–15

0 = No effect.

1 = Clears a bit in the register.

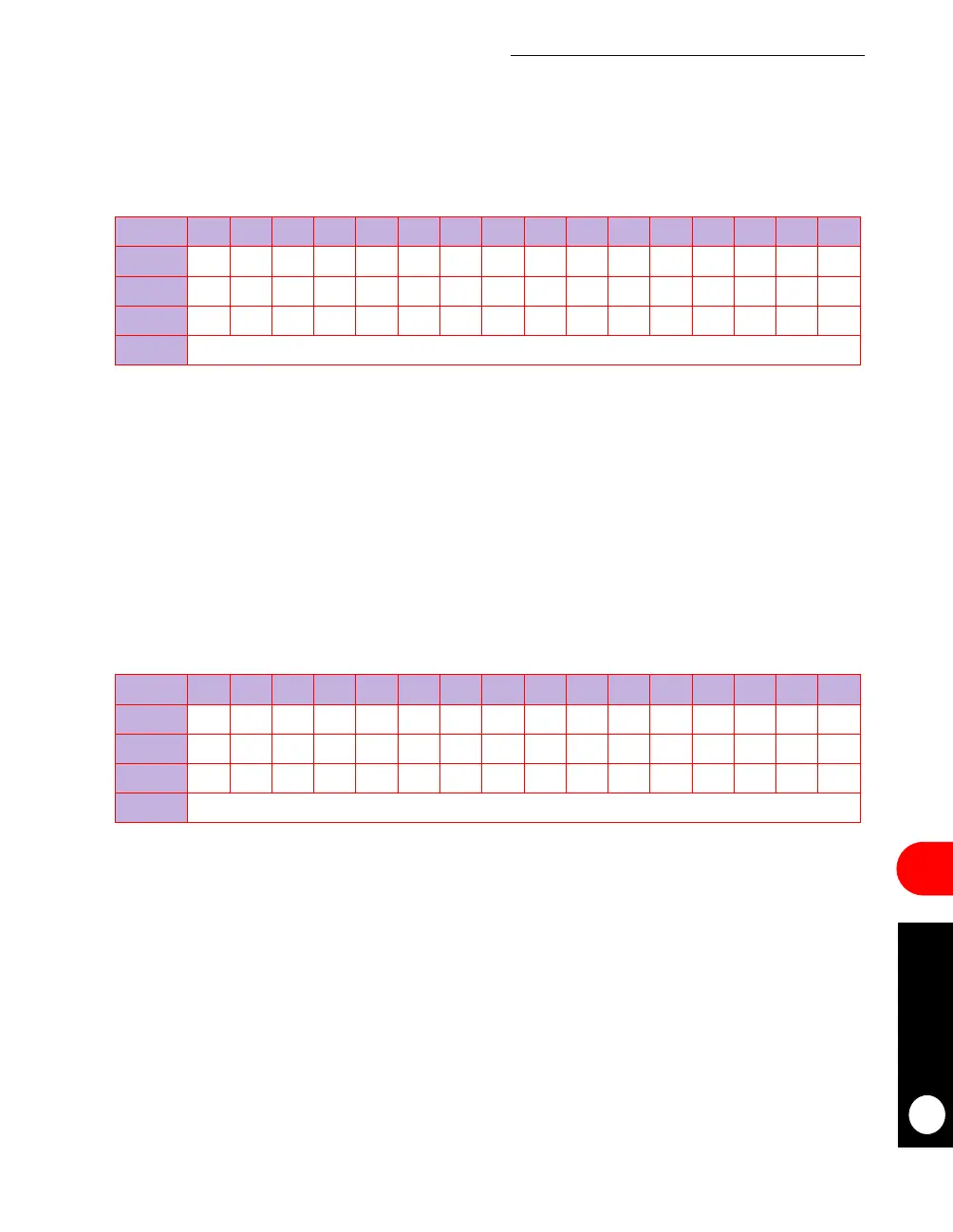

16.2.6.6 RISC TIMER MASK REGISTER. This 16-bit read/write RISC timer mask register

(RTMR) is used to enable interrupts that can be generated in the RTER. If a bit is set, it

enables the corresponding interrupt in the RTER. If a bit is cleared, this register masks the

corresponding interrupt in the RTER. However, an interrupt is only generated if the R-TT bit

is set in the CPM interrupt mask register (CIMR), which is described in

Section 16.15.5.3 CPM Interrupt Mask Register.

TMR0–15—Timer 0–15

0 = Masks the corresponding interrupt in the RTER.

1 = Enables the corresponding interrupt in the RTER.

RTER

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

TMR15 TMR14 TMR13 TMR12 TMR11 TMR10 TMR9 TMR8 TMR7 TMR6 TMR5 TMR4 TMR3 TMR2 TMR1 TMR0

RESET

0000000000000000

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0x9D6

RTMR

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

TMR15 TMR14 TMR13 TMR12 TMR11 TMR10 TMR9 TMR8 TMR7 TMR6 TMR5 TMR4 TMR3 TMR2 TMR1 TMR0

RESET

0000000000000000

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0x9DA

Loading...

Loading...