Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-103

IDMA

COMMUNICATION

16

PROCESSOR MODULE

Regardless of the source size, destination size, source starting address, or destination

starting address, IDMA uses the most efficient packing algorithm possible to perform the

transfer in the lowest number of bus cycles.

16.6.3.11.3 Single-Address Mode (Fly-By Transfers). Each IDMA channel can be

independently programmed to provide single-address transfers. The internal storage is not

used by IDMA, since the transfer occurs directly from a device to memory. This mode is

often referred to as fly-by mode because the internal storage is not used. The external

request is used to start a transfer when the single-address mode is selected. The TYPE field

in the DCMR controls whether a source read or destination write cycle occurs on the data

bus. If the TYPE field is set to 01, the external handshake signals are used with the

destination data buffer pointer and a single-address destination write occurs. If the TYPE

field is set to 10, the external handshake signals are used with the source data buffer pointer

and a single-address source read occurs. There are two types of single-address mode

cycles:

• Single-address source read—During this type of IDMA cycle, the device or memory

selected by the address in the SAPR, the ATx field in the SFCR, and the SIZE field in

the DCMR provides the data and control signals on the data bus. This bus cycle

operates like a normal read bus cycle. The destination device is controlled by the

DREQx

and SDACKx signals. Asserting SDACKx gives you write control to the

destination device. For more details about IDMA handshake signals, refer to

Section 16.6.2 IDMA Interface Signals. For specific timing parameters, visit our

website.

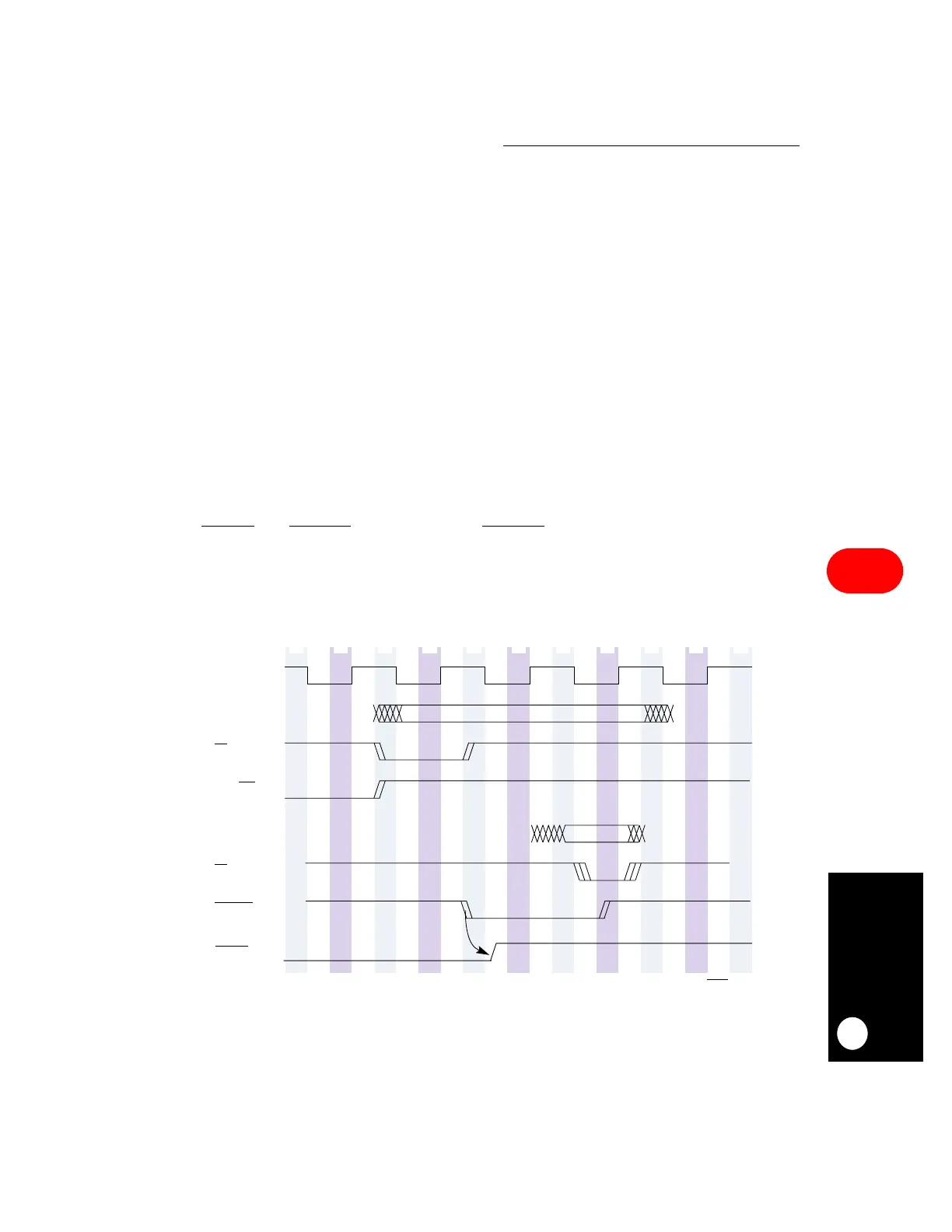

Figure 16-39. Single-Address, Peripheral Write, Asynchronous TA

T3T1T3T1T3

CLKOUT

T1 T3 T1 T3 T1 T3

ADDRESS

RD /

WR

TS

DATA

TA

SDACKx

T0 T2 T0

DREQx

Loading...

Loading...