Communication Processor Module

16-104 MPC823e REFERENCEMANUAL MOTOROLA

IDMA

COMMUNICATION

16

PROCESSOR MODULE

• Single address destination write—During this type of IDMA cycle, the source device is

controlled by the IDMA handshake signals (DREQx

and SDACKx). When the source

device requests service from the IDMA channel, IDMA asserts SDACKx

to allow the

source device to drive data onto the data bus. The data is written to the device or

memory selected by the AT field in the DAPR, the destination AT field in the DFCR, and

the SIZE field in the DCMR. The data bus is driven to three-state for this write cycle. For

more details about IDMA handshake signals, refer to Section 16.6.2 IDMA Interface

Signals. For specific timing parameters, visit our website.

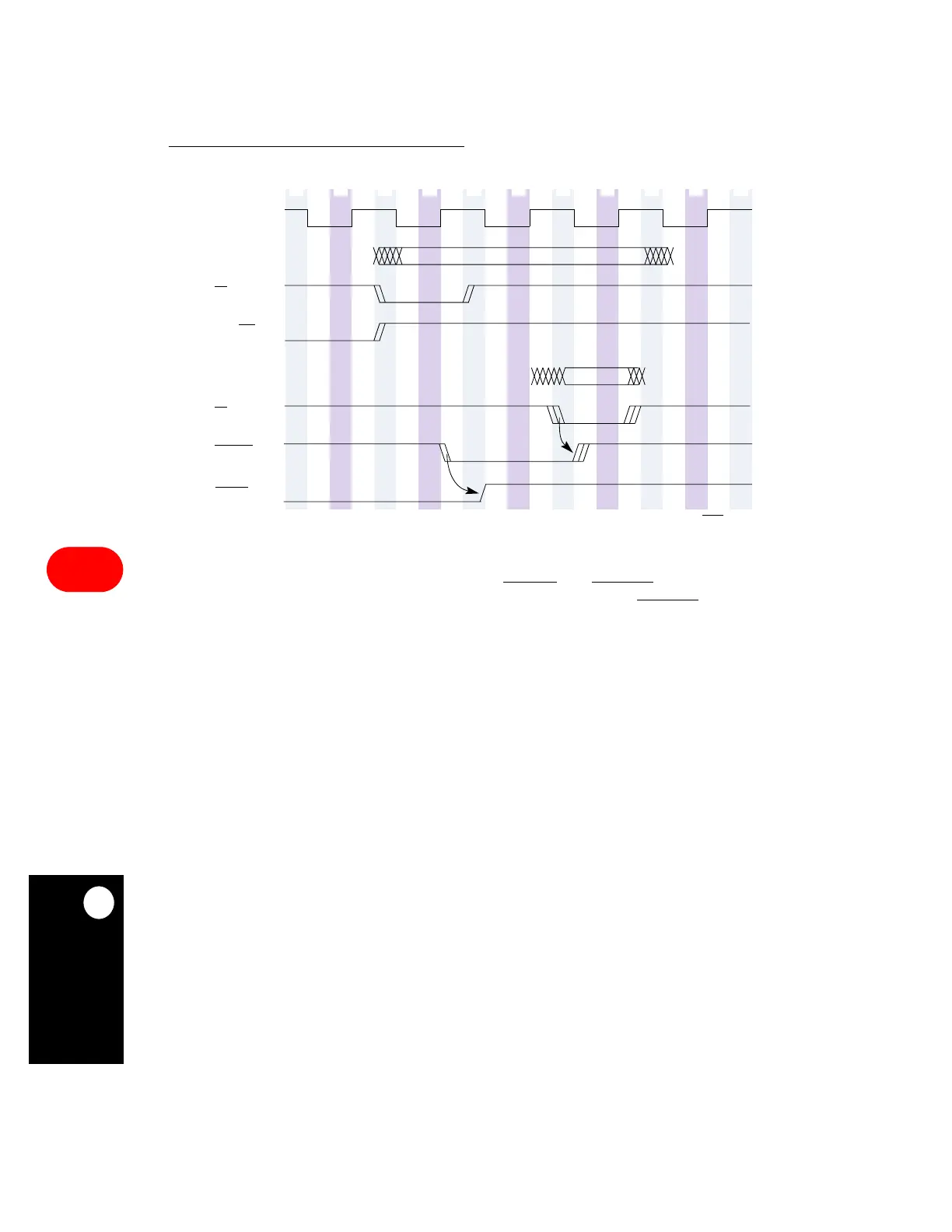

Figure 16-40. Single-Address, Peripheral Write, Synchronous TA

T3T1T3T1T3

CLKOUT

T1 T3 T1 T3 T1 T3

ADDRESS

RD /

WR

TS

DATA

TA

SDACKx

T0 T2 T0

DREQx

Loading...

Loading...