Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-107

IDMA

COMMUNICATION

16

PROCESSOR MODULE

You must initialize the parameter RAM values before the channel is enabled. However, they

must only be modified when there is no DMA activity.

• Buffer Address Pointer—The buffer address pointer (BAPR) contains 32 address bits

of the destination buffer address used by the IDMA. The BAPR must be programmed

to burst-aligned address. In progressive mode, the BAPR is incremented by 16 bytes

after each transfer and it is incremented by 16 for each burst. In interlaced mode the

BAPR is incremented by 16 for each burst while it is within a line and then it is

incremented by the raw bytes register to point to the next line.

• Byte Count Register—The 32-bit byte count register (BCR) specifies the number of

bytes to be transferred by the IDMA. The BCR is decremented by 16 bytes after each

transfer and must be programmed as a multiple of 16. In progressive mode, the IDMA

channel will terminate the transfer of a block of data if this register reaches zero during

operation.

• DMA Channel Mode Register—The 32-bit DMA channel mode register (DCMR)

controls the channel operation mode.

MB1—Must Be 1

For DMA operation, this bit must be set to 1.

Bits 1–2, 9

—

11, 16

—

31—Reserved

These bits are reserved and must be set to 0.

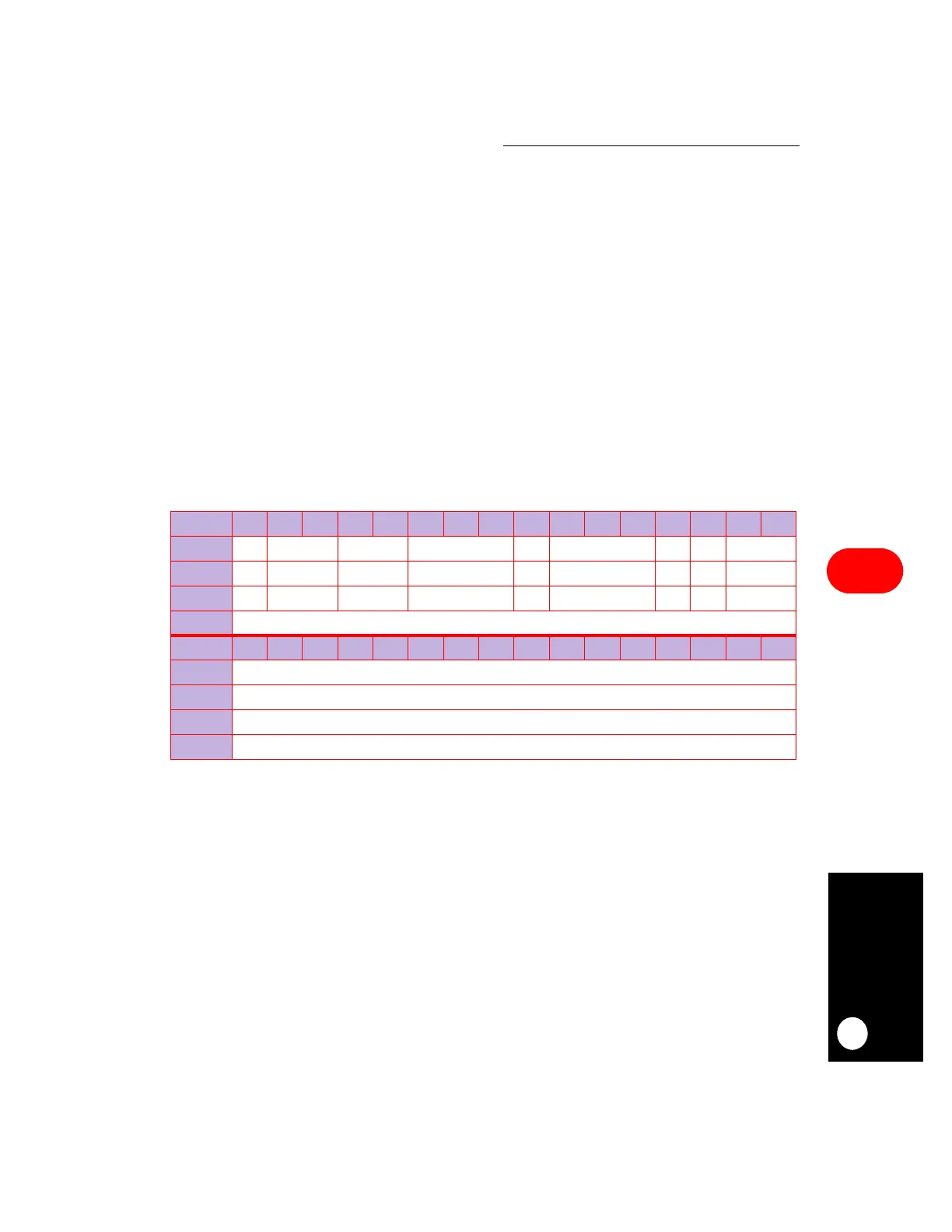

DCMR

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

MB1 RESERVED BO AT STR RESERVED EDGE ITLC BPR

RESET

000 000000

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0x3CC8

BIT 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

RESERVED

RESET

0

R/W

R/W

ADDR

(IMMR & 0xFFFF0000) + 0x3CCA

Loading...

Loading...