Communication Processor Module

16-128

MPC823e REFERENCE MANUAL

MOTOROLA

SERIAL

I/F

COMMUNICATION

16

PROCESSOR MODULE

16.7.5 Serial Interface Programming Model

16.7.5.1 SERIAL INTERFACE GLOBAL MODE REGISTER.

The 8-bit, memory-mapped,

read/write serial interface global mode register (SIGMR) defines the RAM division modes.

Bits 0–3—Reserved

These bits are reserved and must be set to 0.

ENB—Enable Channel B

0 = Channel B is disabled. The serial interface RAMs and TDM routing are in a state

of reset, but all other serial interface functions still operate.

1 = The serial interface is enabled.

ENA—Enable Channel A

0 = Channel A is disabled. The serial interface RAMs and TDM routing are in a state

of reset, but all other serial interface functions still operate.

1 = The serial interface is enabled.

RDM—RAM Division Mode

This field defines the RAM division mode and the number of multiplexed channels supported

in the serial interface.

00 = The serial interface supports one TDM channel with 64 entries for receive routing

and another 64 for transmit routing.

01 = The serial interface supports one TDM channel with 32 entries for receive routing

and another 32 for transmit routing. There are an additional 32 shadow entries for

the receive routing and 32 more for transmit routing that can be used to

dynamically change the routing.

10 = The serial interface supports two TDM channels with 32 entries for receive routing

and another 32 for transmit routing for each of the TDMs.

11 = The serial interface supports two TDM channels with 16 entries for receive routing

and another 16 for transmit routing for each channel. There are an additional 16

shadow entries for the receive routing and 16 more for transmit routing that can

be used to dynamically change the channel routing.

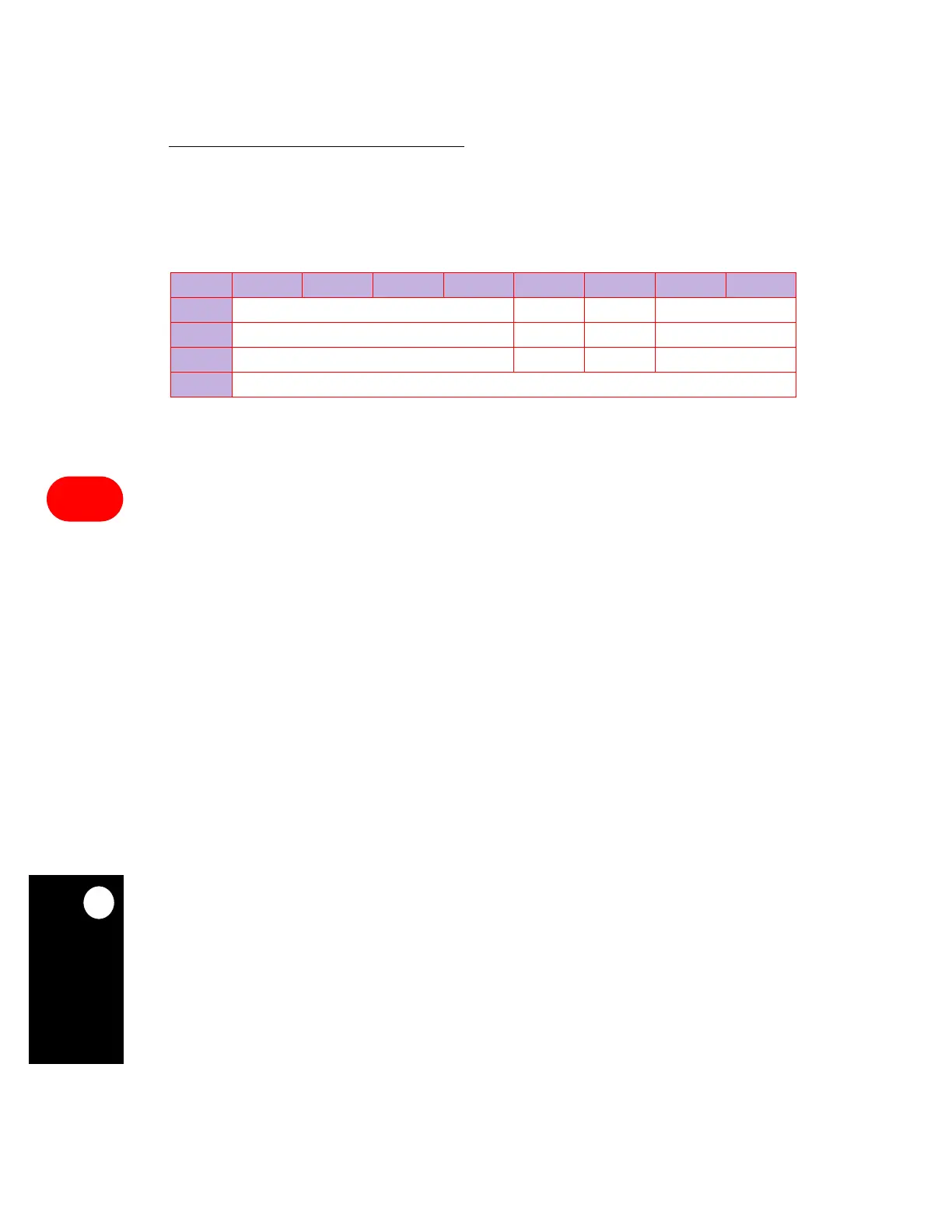

SIGMR

BIT

0 1 2 3 4 5 6 7

FIELD

RESERVED ENB ENA RDM

RESET

0000

R/W

R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0xAE4

Loading...

Loading...