Communication Processor Module

16-144 MPC823e REFERENCE MANUAL MOTOROLA

SERIAL

I/F

COMMUNICATION

16

PROCESSOR MODULE

• TBPTR contains the address of the currently active TXB entry. If the pointer has a value

from 0–15, the current-route RAM is SI RAM address block 192–223 and the CROTB

bit is set to 0 in the SISTR. If the pointer has a value from 224–255, the current-route

RAM is SI RAM address block 160–191 and CROTB is set to 1 in the SISTR.

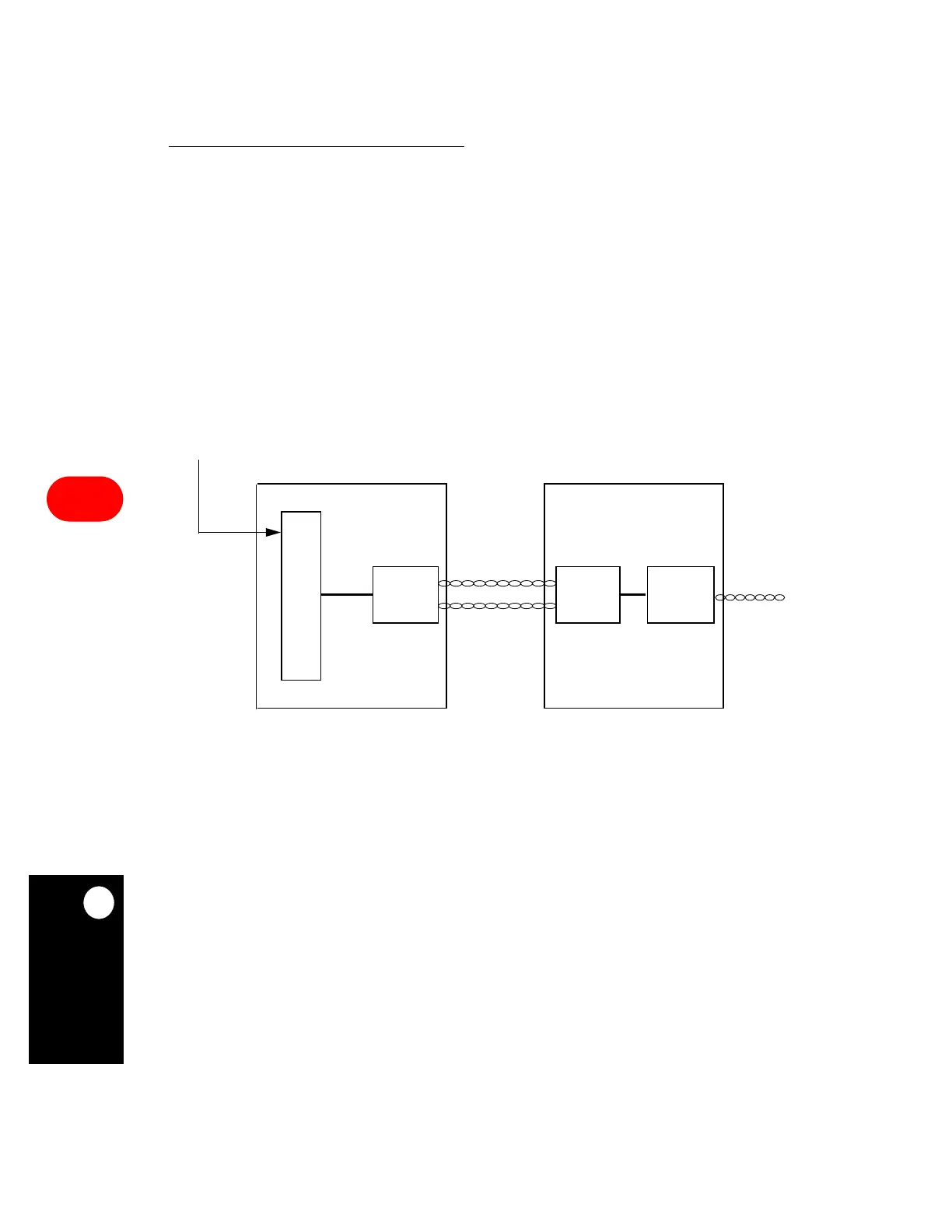

16.7.6 IDL Interface Operation

The full-duplex ISDN interchip digital link (IDL) interface is used to connect a physical layer

device to the MPC823e. The basic and primary rate of the IDL bus is supported by the

MPC823e. In the basic rate of IDL, data on three channels (B1, B2, and D) is transferred in

a 20-bit frame, providing 160kbps full-duplex bandwidth. The MPC823e is an IDL slave

device that is clocked by the IDL bus master (physical layer device) and has separate

receive and transmit sections. The MPC823e supports one IDL bus as illustrated in

Figure 16-58.

MPC823e

Figure 16-58. IDL Bus Application Example

S/T

U

S/T

IDL1

S/T

INTERFACE

ISDN TE NT

U

INTERFACE

INTERFACE INTERFACE

INTERFACE

Loading...

Loading...